|

logicname sample

{ -------------------------------------- }

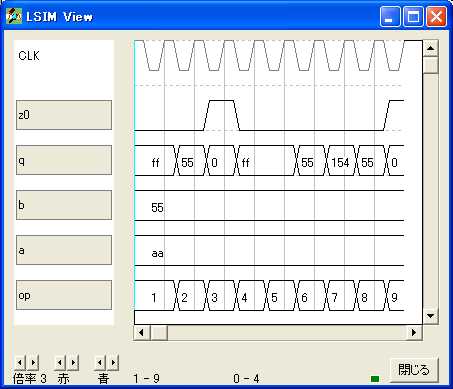

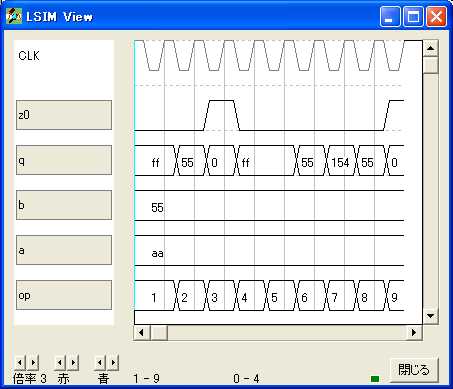

{ 実効譜 }

{ -------------------------------------- }

entity alu

input op[4];

input a[8],b[8];

output q[9];

output z;

bitn pa[9],pb[9];

bitn nq[9];

pa.0:7 = a.0:7;

pb.0:7 = b.0:7;

switch(op)

case 1: {加算}

nq = pa + pb;

case 2: {減算}

nq = pa - pb;

case 3: {論理積}

nq = pa & pb;

case 4: {論理和}

nq = pa | pb;

case 5: {排他的論理和}

nq = pa ^ pb;

case 6: {論理否定}

nq = !a;

case 7: {上桁移動}

nq.1:8 = pa.0:7 ;

case 8: {下桁移動}

nq.0:6 = pa.1:7;

endswitch

if (nq.0:7==0) z = 1; endif

q =nq;

ende

{ -------------------------------------- }

{ 機能実行譜 }

{ -------------------------------------- }

entity sim

output op[4];

output a[8],b[8];

output q[9];

output z;

bitr tc[16];

part alu(op,a,b,q,z)

tc=tc+1;

op=tc.0:3; {←演算の指定}

a=0xaa; {←入力 a}

b=0x55; {←入力 b}

ende

endlogic

|

|