logicname sample

entity main

input reset;

output q[4];

bitr qr[4]; {←記憶信号です。}

if (reset)

qr=0; {←初期化する数値です。}

else

qr=qr; {←初期化後の数値を記憶しています。}

endif

q=qr;

ende

endlogic

|

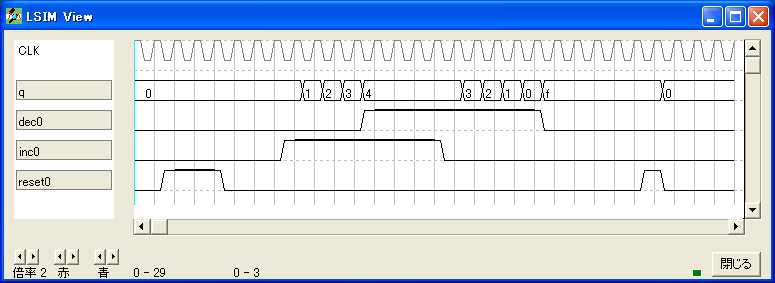

logicname sample

{ -------------------------------------- }

{ 実効譜 }

{ -------------------------------------- }

entity count

input reset;

input inc,dec;

output q[4];

bitr qr[4];

if (reset)

qr=0;

else

if (inc)

qr=qr+1;

else

if (dec)

qr=qr-1;

else

qr=qr;

endif

endif

endif

q=qr;

ende

{ -------------------------------------- }

{ 機能実行譜 }

{ -------------------------------------- }

entity sim

output reset;

output inc,dec;

output q[4];

bitr tc[8];

part count(reset,inc,dec,q)

tc=tc+1;

if (tc>3)

if (tc==25)

reset=1;

else

reset=0;

endif

else

reset=1;

endif

if ((tc>6)&(tc<15)) inc=1; endif

if ((tc>10)&(tc<20)) dec=1; endif

ende

endlogic

|

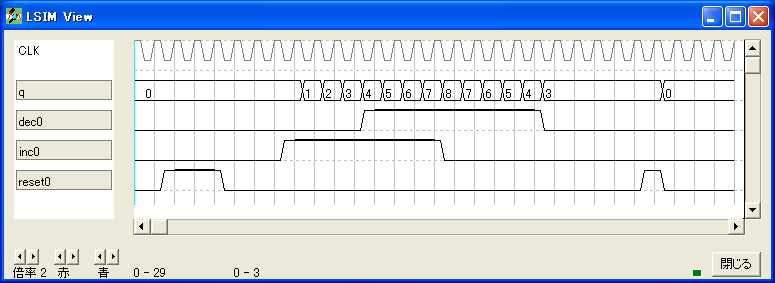

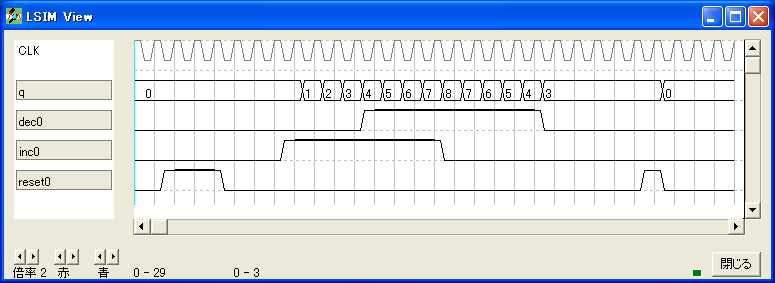

logicname sample

{ -------------------------------------- }

{ 実効譜 }

{ -------------------------------------- }

entity count

input reset;

input inc,dec;

output q[4];

bitr qr[4];

if (reset)

qr=0;

else

if (inc & dec)

qr=qr; {←計数しません}

else

if (inc)

qr=qr+1;

else

if (dec)

qr=qr-1;

else

qr=qr;

endif

endif

endif

endif

q=qr;

ende

{ -------------------------------------- }

{ 機能実行譜 }

{ -------------------------------------- }

entity sim

output reset;

output inc,dec;

output q[4];

bitr tc[8];

part count(reset,inc,dec,q)

tc=tc+1;

if (tc>3)

if (tc==25)

reset=1;

else

reset=0;

endif

else

reset=1;

endif

if ((tc>6)&(tc<15)) inc=1; endif

if ((tc>10)&(tc<20)) dec=1; endif

ende

endlogic

|