|

logicname sample

{ -------------------------------------- }

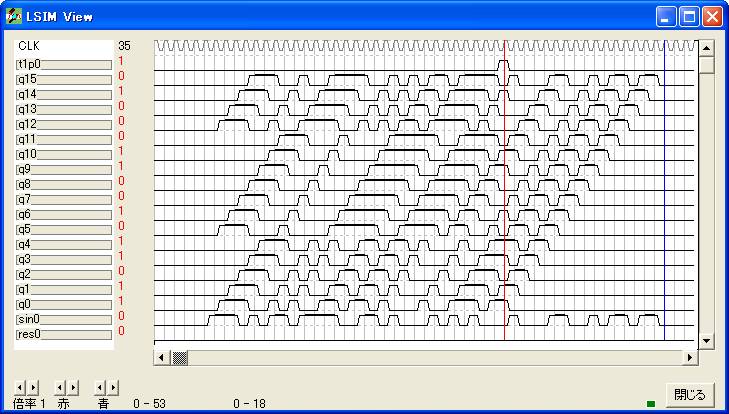

{ 実効譜 }

{ -------------------------------------- }

entity crc16

input res;

input sin;

output q[16];

bitr rq[16];

if (res)

rq = 0;

else

rq.0 = rq.15 ^ sin;

rq.5 = rq.4 ^ (rq.15 ^ sin);

rq.12 = rq.11 ^ (rq.15 ^ sin);

rq.1:4 = rq.0:3;

rq.6:11 = rq.5:10;

rq.13:15 = rq.12:14;

endif

q = rq;

ende

{ -------------------------------------- }

{ 機能実行譜 }

{ -------------------------------------- }

entity sim

output res;

output sin;

output q[16];

output t1p;

bitr tc[8];

bitr td[28];

bitr cd[16];

part crc16(res,sin,q)

tc=tc+1;

if (tc>3)

td.1:27=td.0:26;

else {↓テストデータ}

td.0:27=0b0111010110111100110100010101;

endif

if (tc>=34)

cd.1:15=cd.0:14;

else {↓テストCRC}

cd=0b0100011001011011;

endif

if (tc==34) t1p=1; endif {←テストデータ入力終了}

if (tc>=34)

sin=cd.15; {←CRC入力}

else

sin=td.27; {←テストデータ入力}

endif

ende

endlogic

|

|