|

logicname sample

{ -------------------------------------- }

{ 手続き譜 }

{ -------------------------------------- }

procedure spu

input a;

output q;

bitr rq[2];

switch(rq)

case 0:

if (a) rq = 1; endif

case 1:

rq = 2;

case 2:

if (a)

rq = rq;

else

rq = 0;

endif

endswitch

q = rq.0;

endp

{ -------------------------------------- }

{ 手続き譜 }

{ -------------------------------------- }

procedure spd

input a;

output q;

bitr rq[2];

switch(rq)

case 0:

if (a) rq = 1; endif

case 1:

if (a)

rq = rq;

else

rq = 2;

endif

case 2: rq = 0;

endswitch

q = rq.1;

endp

{ -------------------------------------- }

{ 実効譜 }

{ -------------------------------------- }

entity dep

input a;

output q;

bitr rq;

bitn pu,pd;

bitr c[4];

pu = spu(a);

pd = spd(a);

if (pu | pd)

if (c==2) {←※}

c = 0;

rq = rq + 1;

else

c = c + 1;

rq = rq;

endif

else

c = c;

rq = rq;

endif

q = rq;

ende

{ -------------------------------------- }

{ 機能実行譜 }

{ -------------------------------------- }

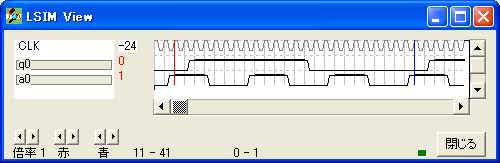

entity sim

output a;

output q;

output c;

bitr tc[4];

part dep(a,q)

tc=tc+1;

a=tc.2;

ende

endlogic

|

|