|

logicname sample

{ -------------------------------------- }

{ 実効譜 }

{ -------------------------------------- }

entity div8

input reset; {初期化}

input a[8]; {被除数}

input b[8]; {除数}

output q[8]; {商}

output p[8]; {余り}

bitr rah[8]; {a 移動上8桁}

bitr ral[8]; {a 移動下8桁}

bitr rq[8]; {商 記憶}

bitr pseq[4]; {計算手順}

if (reset) {←初期化}

rah=0;

ral=a;

rq=0;

pseq=0;

else {↓計算}

if (pseq<=8) {↓計算手順が8未満なら計算}

pseq=pseq+1; {←計算手順を進めます。}

rah.0=ral.7; {←aを上位に桁移動}

ral.1:7=ral.0:6;

if (rah>=b) {←a 移動上8桁とbが同じかaが大きい場合は}

rah=(rah-b)>>1; {bを減算して桁移動します。}

else {←a 移動上8桁よりbが大きい場合は桁移動だけします。}

rah.1:7=rah.0:6;

endif

if (rah>=b) {←a 移動上8桁とbが同じかaが大きい場合は}

rq.0=1; {←商の最下位の桁を1にします。}

endif

rq.1:7=rq.0:6;{←商を上位に桁移動}

else {↓計算手順が8以上なら停止}

pseq=pseq;

rah=rah;

ral=ral;

rq=rq;

endif

endif

q=rq; {商の代入}

p.0:6=rah.1:7; {余りの代入}

p.7=0;

ende

{ -------------------------------------- }

{ 機能実行譜 }

{ -------------------------------------- }

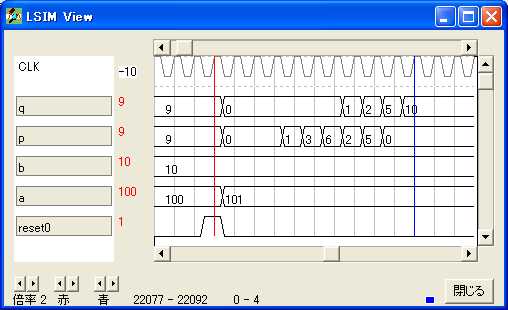

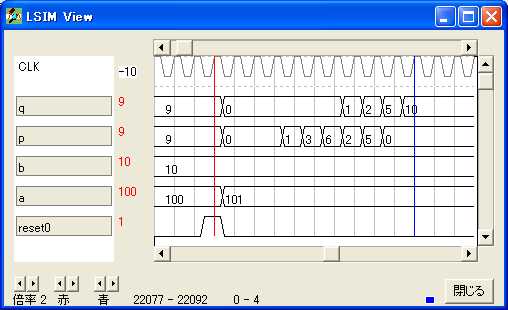

entity sim

output reset;

output a[8],b[8];

output q[8];

output p[8];

bitr tc[4];

bitr tca[8];

bitr tcb[8];

part div8(reset,a,b,q,p)

tc=tc+1;

if (tc==15) tca=tca+1; else tca=tca; endif

if ((tc==15)&(tca==255))

tcb=tcb+1;

else

if ((tc==15)&(tcb==0))

tcb=5;

else

tcb=tcb;

endif

endif

reset=(tc==15);

a=tca;

b=tcb;

ende

endlogic

|