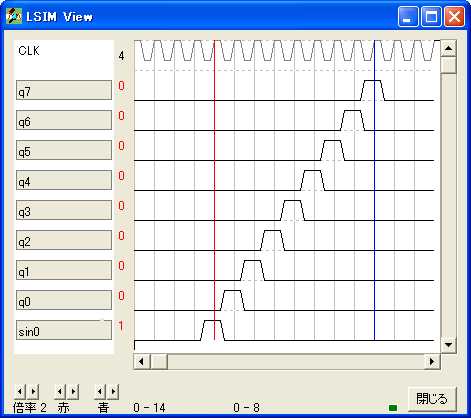

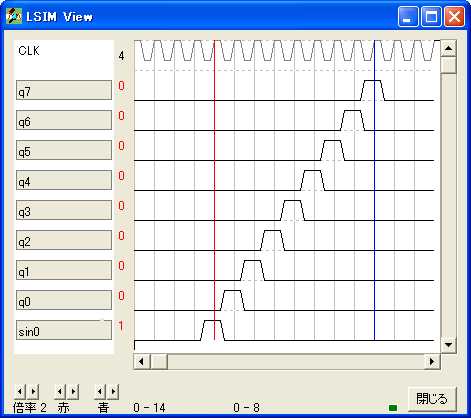

logicname sample

{ -------------------------------------- }

{ 実効譜 }

{ -------------------------------------- }

entity shift

input sin;

output q[8];

bitr rq[8];

rq.0 = sin;

rq.1:7 = rq.0:6;

q=rq;

ende

{ -------------------------------------- }

{ 機能実行譜 }

{ -------------------------------------- }

entity sim

output sin;

output q[8];

bitr tc[4];

part shift(sin,q)

tc=tc+1;

if (tc==3) sin=1; endif

ende

endlogic

|

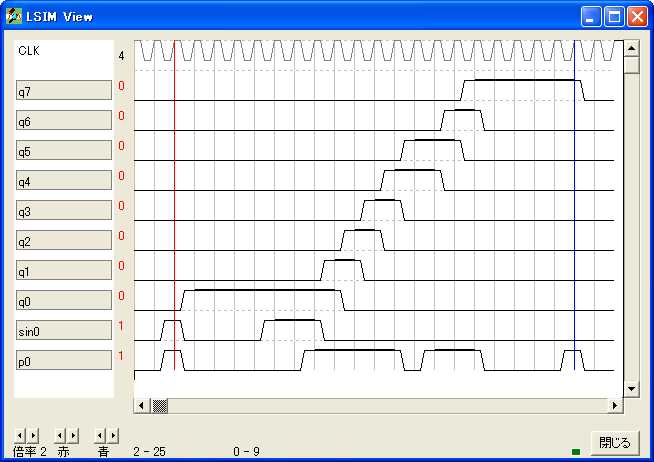

logicname sample

{ -------------------------------------- }

{ 実効譜 }

{ -------------------------------------- }

entity shift

input p;

input sin;

output q[8];

bitr rq[8];

if (p)

rq.0 = sin;

rq.1:7 = rq.0:6;

else

rq = rq;

endif

q=rq;

ende

{ -------------------------------------- }

{ 機能実行譜 }

{ -------------------------------------- }

entity sim

output p;

output sin;

output q[8];

bitr tc[5];

part shift(p,sin,q)

tc=tc+1;

if (tc==3) sin=1; p=1; endif

if ((tc>7)&(tc<11)) sin=1; endif

if ((tc>9)&(tc<15)) p=1; endif

if ((tc>15)&(tc<19)) p=1; endif

if ((tc>22)&(tc<24)) p=1; endif

ende

endlogic

|

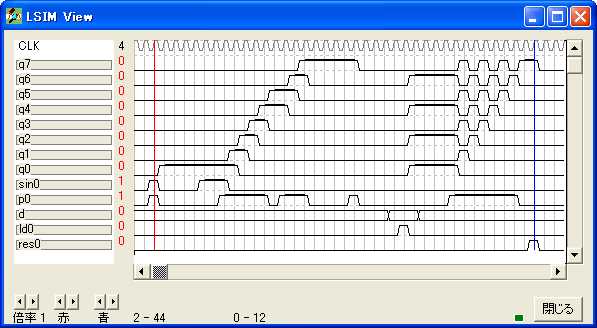

logicname sample

{ -------------------------------------- }

{ 実効譜 }

{ -------------------------------------- }

entity shift

input res,ld;

input d[8];

input p;

input sin;

output q[8];

bitr rq[8];

if (res)

rq = 0;

else

if (ld)

rq = d;

else

if (p)

rq.0 = sin;

rq.1:7 = rq.0:6;

else

rq = rq;

endif

endif

endif

q=rq;

ende

{ -------------------------------------- }

{ 機能実行譜 }

{ -------------------------------------- }

entity sim

output res,ld;

output d[8];

output p;

output sin;

output q[8];

bitr tc[8];

part shift(res,ld,d,p,sin,q)

tc=tc+1;

if (tc==3) sin=1; p=1; endif

if ((tc>7)&(tc<11)) sin=1; endif

if ((tc>9)&(tc<15)) p=1; endif

if ((tc>15)&(tc<19)) p=1; endif

if ((tc>22)&(tc<24)) p=1; endif

if ((tc>26)&(tc<30)) d=0x55; endif

if (tc==28) ld=1; endif

if ((tc>32)&(tc<40)) p=1; endif

if (tc==41) res=1; endif

ende

endlogic

|