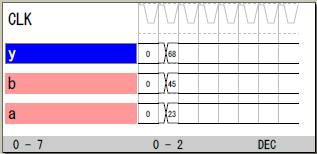

logicname yahoo00

entity main

input a[8];

input b[8];

output y[8];

y=a+b;

ende

entity sim

output a[8];

output b[8];

output y;

part main(a,b)

a=23; { この数値を変えて検証結果を見て下さい。 }

b=45; { 〃 }

ende

endlogic

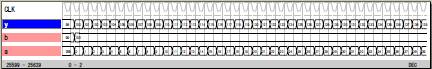

logicname yahoo01

entity main

input a[8];

input b[8];

output y[8];

y=a+b;

ende

entity sim

output a[8];

output b[8];

output y;

bitr tc[17];

part main(a,b)

tc=tc+1;

a=tc.0:7; { 8ビットの全値 }

b=tc.8:15; { 〃 }

ende

endlogic

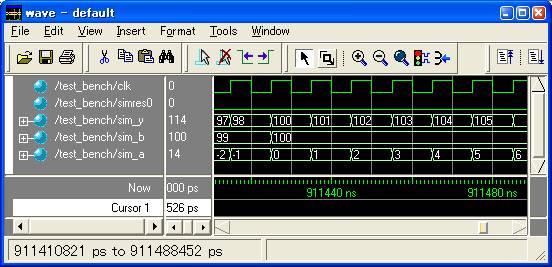

ldc y02 -vr -sp 1000 -bundleXilinxの開発ツールでシミュレーションするために verilogのソースを作ります。 -bundleは信号をまとめて閲覧したいときに指定します。 これでe1.vとs1.vが得られます。e1.vは機能実行譜で s1.vはテストベンチです。

logicname yahoo01

entity main

input a[8];

input b[8];

output y[8];

y=a+b;

ende

entity sim

output a[8];

output b[8];

output y;

input simres; { ModelSIMなどで使う場合に必要 }

bitr tc[17];

part main(a,b)

if (!simres) tc=tc+1; endif { 記憶信号を初期化 }

a=tc.0:7; { 8ビットの全値 }

b=tc.8:15; { 〃 }

ende

endlogic

ldc y03 -vre0.vができているのでこれを使ってXilinxの開発ツール でXC9536のチップデータを作ります。

logicname yahoo03 entity main input a[8]; input b[8]; output y[8]; y=a+b; ende endlogic

module main (

y0 // output

,a0 // input

,b0 // input

,y1 // output

,a1 // input

,b1 // input

,y2 // output

,a2 // input

,b2 // input

,y3 // output

,a3 // input

,b3 // input

,y4 // output

,a4 // input

,b4 // input

,y5 // output

,a5 // input

,b5 // input

,y6 // output

,a6 // input

,b6 // input

,y7 // output

,a7 // input

,b7 // input

);

output y0 ;

input a0 ;

input b0 ;

output y1 ;

input a1 ;

input b1 ;

output y2 ;

input a2 ;

input b2 ;

output y3 ;

input a3 ;

input b3 ;

output y4 ;

input a4 ;

input b4 ;

output y5 ;

input a5 ;

input b5 ;

output y6 ;

input a6 ;

input b6 ;

output y7 ;

input a7 ;

input b7 ;

wire n_n26 ;

wire n_n27 ;

wire n_n28 ;

wire n_n29 ;

wire n_n30 ;

wire n_n31 ;

wire n_n32 ;

// equations

assign y0 = (~a0 & b0)

| (a0 & ~b0) ;

assign n_n26 = (a0 & b0) ;

assign y1 = (~a1 & ~b1 & a0 & b0)

| (~a1 & b1 & ~n_n26)

| (a1 & ~b1 & ~n_n26)

| (a1 & b1 & a0 & b0) ;

assign n_n27 = (~a1 & b1 & a0 & b0)

| (a1 & ~b1 & a0 & b0)

| (a1 & b1) ;

assign y2 = (~a2 & ~b2 & n_n27)

| (~a2 & b2 & ~n_n27)

| (a2 & ~b2 & ~n_n27)

| (a2 & b2 & n_n27) ;

assign n_n28 = (~a2 & b2 & n_n27)

| (a2 & ~b2 & n_n27)

| (a2 & b2) ;

assign y3 = (~a3 & ~b3 & n_n28)

| (~a3 & b3 & ~n_n28)

| (a3 & ~b3 & ~n_n28)

| (a3 & b3 & n_n28) ;

assign n_n29 = (~a3 & b3 & n_n28)

| (a3 & ~b3 & n_n28)

| (a3 & b3) ;

assign y4 = (~a4 & ~b4 & n_n29)

| (~a4 & b4 & ~n_n29)

| (a4 & ~b4 & ~n_n29)

| (a4 & b4 & n_n29) ;

assign n_n30 = (~a4 & b4 & n_n29)

| (a4 & ~b4 & n_n29)

| (a4 & b4) ;

assign y5 = (~a5 & ~b5 & n_n30)

| (~a5 & b5 & ~n_n30)

| (a5 & ~b5 & ~n_n30)

| (a5 & b5 & n_n30) ;

assign n_n31 = (~a5 & b5 & n_n30)

| (a5 & ~b5 & n_n30)

| (a5 & b5) ;

assign y6 = (~a6 & ~b6 & n_n31)

| (~a6 & b6 & ~n_n31)

| (a6 & ~b6 & ~n_n31)

| (a6 & b6 & n_n31) ;

assign n_n32 = (~a6 & b6 & n_n31)

| (a6 & ~b6 & n_n31)

| (a6 & b6) ;

assign y7 = (~a7 & ~b7 & n_n32)

| (~a7 & b7 & ~n_n32)

| (a7 & ~b7 & ~n_n32)

| (a7 & b7 & n_n32) ;

endmodule

|

library IEEE;

use IEEE.std_logic_1164.all;

entity main is

port(y0 : out std_logic;

a0 : in std_logic;

b0 : in std_logic;

y1 : out std_logic;

a1 : in std_logic;

b1 : in std_logic;

y2 : out std_logic;

a2 : in std_logic;

b2 : in std_logic;

y3 : out std_logic;

a3 : in std_logic;

b3 : in std_logic;

y4 : out std_logic;

a4 : in std_logic;

b4 : in std_logic;

y5 : out std_logic;

a5 : in std_logic;

b5 : in std_logic;

y6 : out std_logic;

a6 : in std_logic;

b6 : in std_logic;

y7 : out std_logic;

a7 : in std_logic;

b7 : in std_logic);

end main;

architecture RTL of main is

signal n_n26 : std_logic ;

signal n_n27 : std_logic ;

signal n_n28 : std_logic ;

signal n_n29 : std_logic ;

signal n_n30 : std_logic ;

signal n_n31 : std_logic ;

signal n_n32 : std_logic ;

begin

y0 <= (not a0 and b0)

or (a0 and not b0) ;

n_n26 <= (a0 and b0) ;

y1 <= (not a1 and not b1 and a0 and b0)

or (not a1 and b1 and not n_n26)

or (a1 and not b1 and not n_n26)

or (a1 and b1 and a0 and b0) ;

n_n27 <= (not a1 and b1 and a0 and b0)

or (a1 and not b1 and a0 and b0)

or (a1 and b1) ;

y2 <= (not a2 and not b2 and n_n27)

or (not a2 and b2 and not n_n27)

or (a2 and not b2 and not n_n27)

or (a2 and b2 and n_n27) ;

n_n28 <= (not a2 and b2 and n_n27)

or (a2 and not b2 and n_n27)

or (a2 and b2) ;

y3 <= (not a3 and not b3 and n_n28)

or (not a3 and b3 and not n_n28)

or (a3 and not b3 and not n_n28)

or (a3 and b3 and n_n28) ;

n_n29 <= (not a3 and b3 and n_n28)

or (a3 and not b3 and n_n28)

or (a3 and b3) ;

y4 <= (not a4 and not b4 and n_n29)

or (not a4 and b4 and not n_n29)

or (a4 and not b4 and not n_n29)

or (a4 and b4 and n_n29) ;

n_n30 <= (not a4 and b4 and n_n29)

or (a4 and not b4 and n_n29)

or (a4 and b4) ;

y5 <= (not a5 and not b5 and n_n30)

or (not a5 and b5 and not n_n30)

or (a5 and not b5 and not n_n30)

or (a5 and b5 and n_n30) ;

n_n31 <= (not a5 and b5 and n_n30)

or (a5 and not b5 and n_n30)

or (a5 and b5) ;

y6 <= (not a6 and not b6 and n_n31)

or (not a6 and b6 and not n_n31)

or (a6 and not b6 and not n_n31)

or (a6 and b6 and n_n31) ;

n_n32 <= (not a6 and b6 and n_n31)

or (a6 and not b6 and n_n31)

or (a6 and b6) ;

y7 <= (not a7 and not b7 and n_n32)

or (not a7 and b7 and not n_n32)

or (a7 and not b7 and not n_n32)

or (a7 and b7 and n_n32) ;

end RTL;

|