計数器

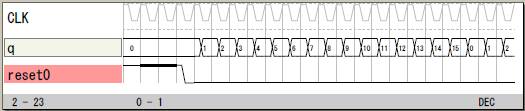

その1

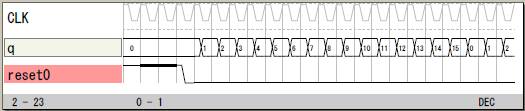

チップCLKを数える計数器です。

実効譜は初期化の付いたチップCLKを計数するだけの

最も単純な計数器です。

file: sample04

論理譜

logicname yahoo05

entity main

input reset;

output q[4];

bitr a[4];

if (reset)

a=0;

else

a=a+1;

endif

q=a;

ende

entity sim

output reset;

output q[4];

bitr tc[8];

part main(reset)

tc=tc+1;

if (tc<5) reset=1; endif

ende

endlogic

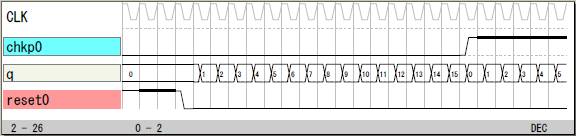

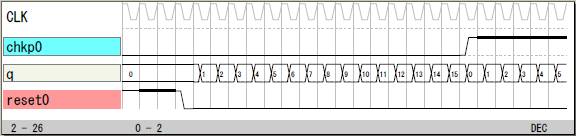

その2

機能実行譜で実効譜の出力を検査して結果を保存できます。

機能実行譜の論理は実効譜の入力に値を与えるだけでなく

実効譜の出力を監視して、それに対応した動作をするこが

できます。

機能実行譜はqを監視してqが15になったらchkpに1を記憶

します。

file: sample05

論理譜

logicname yahoo06

entity main

input reset;

output q[4];

bitr a[4];

if (reset)

a=0;

else

a=a+1;

endif

q=a;

ende

entity sim

output reset;

output q[4];

output chkp;

bitr tc[8];

bitr chkpreg;

bitn node_q[4];

bitn node_reset;

reset=node_reset;

chkp=chkpreg;

q=node_q;

part main(node_reset,node_q)

tc=tc+1;

if (tc<5) node_reset=1; endif

if (node_reset)

chkpreg=0;

else

if (node_q==15)

chkpreg=1;

else

chkpreg=chkpreg;

endif

endif

ende

endlogic

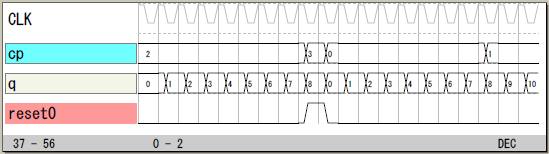

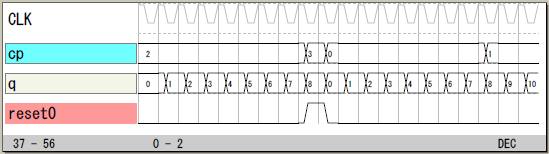

その3

実効譜の出力に機能実行譜が応答できます。

実効譜の出力に機能実行譜が応答して実効譜に与える

入力値を変えることができます。

本機能実行譜ではqが7になるときを計数して3回目に

7になったときresetを1にするようにしています。

機能実行譜はチップ化される実効譜の外にある論理的

な動作を実行することが目的の譜です。

このために実効譜に与える入力値を実効譜の出力によ

って動的に変えることができるようになっています。

file: sample06

論理譜

logicname yahoo07

entity main

input reset;

output q[4];

bitr a[4];

if (reset)

a=0;

else

a=a+1;

endif

q=a;

ende

entity sim

output reset;

output q[4];

output cp[2];

bitr tc[8];

bitr chkcount[2];

bitr chkp[2];

bitn node_q[4];

bitn node_reset;

reset=node_reset;

cp=chkp;

q=node_q;

part main(node_reset,node_q)

tc=tc+1;

if (tc<5)

node_reset=1;

else

if (chkp==3) node_reset=1; endif { qが3回目の7になったときにリセット }

endif

if (node_q==7)

chkp=chkp+1;

else

if (node_reset)

chkp=0;

else

chkp=chkp;

endif

endif

ende

endlogic

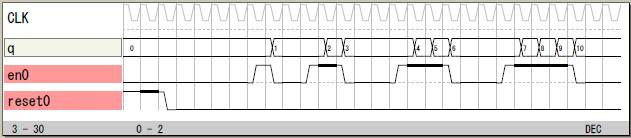

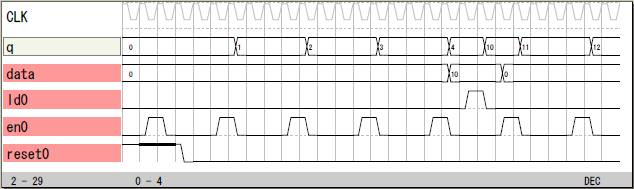

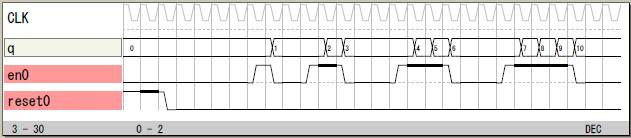

その4

動かしたり止めたりする信号を付けます。

enが1のときに計数を行い0のとき停止します。

同期式の論理ではenのような信号を使ってある程度のまと

まりを持った論理どうしの歩調をとります。

file: sample07

論理譜

logicname yahoo08

entity main

input reset;

input en;

output q[4];

bitr a[4];

if (reset)

a=0;

else

if (en)

a=a+1;

else

a=a;

endif

endif

q=a;

ende

entity sim

output reset;

output en;

output q[4];

bitr tc[8];

part main(reset,en,q)

tc=tc+1;

if (tc<5) reset=1; endif

if (tc==10) en=1; endif

if ((tc>12)&(tc<15)) en=1; endif

if ((tc>17)&(tc<21)) en=1; endif

if ((tc>23)&(tc<28)) en=1; endif

ende

endlogic

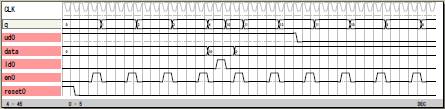

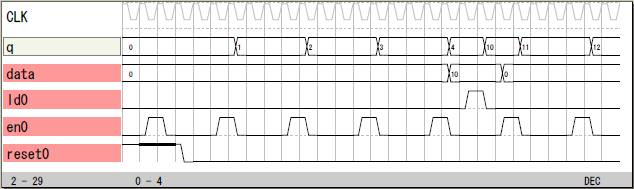

その5

計数値を設定できる計数器です。

ldが1のときにqにdataを代入して記憶します。

file: sample08

論理譜

logicname yahoo08

entity main

input reset;

input en;

input ld;

input data[4];

output q[4];

bitr a[4];

if (reset)

a=0;

else

if (ld)

a=data;

else

if (en)

a=a+1;

else

a=a;

endif

endif

endif

q=a;

ende

entity sim

output reset;

output en;

output ld;

output data[4];

output q[4];

bitr tc[8];

part main(reset,en,ld,data,q)

tc=tc+1;

if (tc<5) reset=1; endif

if (tc.0:1==3) en=1; endif

if (tc==21) ld=1; endif

if ((tc>19)&(tc<23)) data=10; endif

ende

endlogic

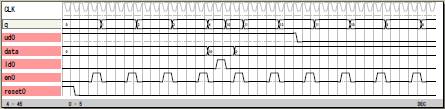

その6

増やしたり減らしたりできる計数器です。

その5の計数器にudを追加してudが1のとき増数、0のとき

減数しています。

file: sample09

論理譜

logicname yahoo08

entity main

input reset;

input en;

input ld;

input data[4];

input ud;

output q[4];

bitr a[4];

if (reset)

a=0;

else

if (ld)

a=data;

else

if (en)

if (ud)

a=a+1;

else

a=a-1;

endif

else

a=a;

endif

endif

endif

q=a;

ende

entity sim

output reset;

output en;

output ld;

output data[4];

output ud;

output q[4];

bitr tc[8];

part main(reset,en,ld,data,ud,q)

tc=tc+1;

if (tc<5) reset=1; endif

if (tc.0:1==3) en=1; endif

if (tc==21) ld=1; endif

if ((tc>19)&(tc<23)) data=10; endif

if (tc>29) ud=0; else ud=1; endif

ende

endlogic