Ś▌ÄZŖĒ

é╗é╠1

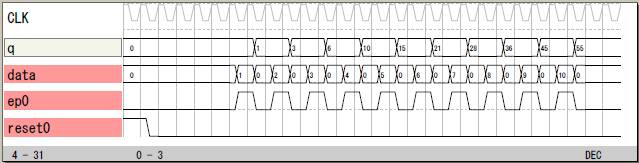

8ārābāgé╠Ś▌ÄZŖĒé┼éĘüB

epé¬1é╠éŲé½é╠dataéqé╔æ½éĄé▄éĘüB

file: sample14

ś_ŚØĢł

logicname yahoo15

entity main

input reset;

input ep;

input data[8];

output q[8];

bitr acc[8];

if (reset)

acc=0;

else

if (ep)

acc=acc+data;

else

acc=acc;

endif

endif

q=acc;

ende

entity sim

output reset;

output ep;

output data[8];

output q[8];

bitr tc[8];

part main(reset,ep,data,q)

tc=tc+1;

if (tc<5) reset=1; endif

switch(tc)

case 10: ep=1; data=1;

case 12: ep=1; data=2;

case 14: ep=1; data=3;

case 16: ep=1; data=4;

case 18: ep=1; data=5;

case 20: ep=1; data=6;

case 22: ep=1; data=7;

case 24: ep=1; data=8;

case 26: ep=1; data=9;

case 28: ep=1; data=10;

endswitch

ende

endlogic

é╗é╠2

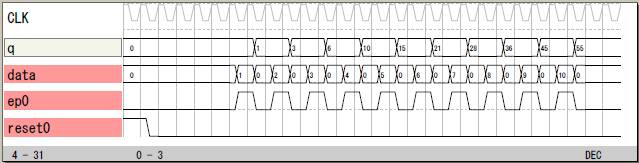

æ½éĄéĮéĶł°éóéĮéĶé┼é½éķŚ▌ÄZŖĒé┼éĘüB

pé¬0é╠éŲé½é╔æ½éĄé▄éĘüApé¬1é╠éŲé½é╔ł°é½é▄éĘüB

file: sample15

ś_ŚØĢł

logicname yahoo16

entity main

input reset;

input ep;

input data[8];

input p;

output q[8];

bitr acc[8];

if (reset)

acc=0;

else

if (ep)

if (p)

acc=acc-data;

else

acc=acc+data;

endif

else

acc=acc;

endif

endif

q=acc;

ende

entity sim

output reset;

output ep;

output data[8];

output q[8];

output p;

bitr tc[8];

part main(reset,ep,data,p,q)

tc=tc+1;

if (tc<5) reset=1; endif

if ((tc>=10)&(tc<=28)) p=0; endif

if ((tc>=30)&(tc<=48)) p=1; endif

switch(tc)

case 10: ep=1; data=1;

case 12: ep=1; data=2;

case 14: ep=1; data=3;

case 16: ep=1; data=4;

case 18: ep=1; data=5;

case 20: ep=1; data=6;

case 22: ep=1; data=7;

case 24: ep=1; data=8;

case 26: ep=1; data=9;

case 28: ep=1; data=10;

endswitch

switch(tc)

case 30: ep=1; data=1;

case 32: ep=1; data=2;

case 34: ep=1; data=3;

case 36: ep=1; data=4;

case 38: ep=1; data=5;

case 40: ep=1; data=6;

case 42: ep=1; data=7;

case 44: ep=1; data=8;

case 46: ep=1; data=9;

case 48: ep=1; data=10;

endswitch

ende

endlogic