並び替え

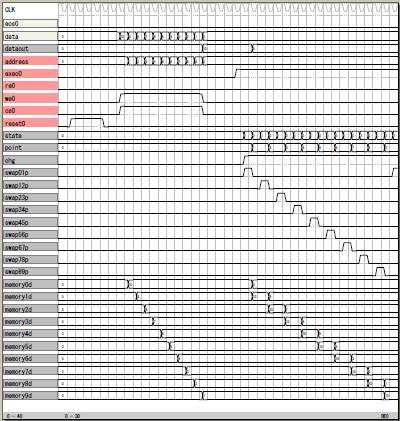

その1

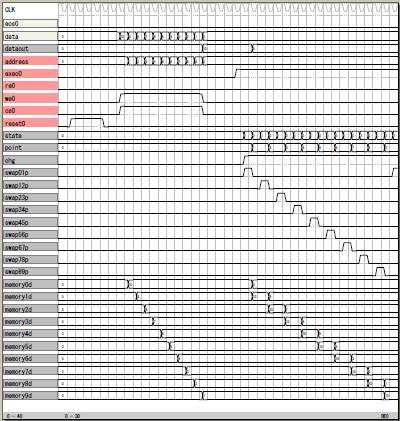

チップ内のメモリのデータを小さい順番に並び替えます。

今回はコンパイルに時間がかかるので最適化を最小限

で回数を1回として圧縮はしない指定でコンパイルしま

す。

並び替えが終わるとeosが1になります。

並び替えの行程を見るために検査端子にメモリの値を出

しています。

file: sample24

論理譜

logicname yahoo33

entity main

input reset;

input cs;

input re;

input we;

input exec;

input address[4];

inout data[8];

output eos;

bitr memory0d[8];

bitr memory1d[8];

bitr memory2d[8];

bitr memory3d[8];

bitr memory4d[8];

bitr memory5d[8];

bitr memory6d[8];

bitr memory7d[8];

bitr memory8d[8];

bitr memory9d[8];

bitr memory10d[8];

bitn datain[8];

bitn dataout[8];

bitn datacnt;

bitr state[3];

bitr count[8];

bitr point[4];

bitr chg;

bitn swap01p;

bitn swap12p;

bitn swap23p;

bitn swap34p;

bitn swap45p;

bitn swap56p;

bitn swap67p;

bitn swap78p;

bitn swap89p;

bitn state0p;

bitn state1p;

bitn stateend;

bitr hit[2];

output T0P[8]; T0P=memory0d;

output T1P[8]; T1P=memory1d;

output T2P[8]; T2P=memory2d;

output T3P[8]; T3P=memory3d;

output T4P[8]; T4P=memory4d;

output T5P[8]; T5P=memory5d;

output T6P[8]; T6P=memory6d;

output T7P[8]; T7P=memory7d;

output T8P[8]; T8P=memory8d;

output T9P[8]; T9P=memory9d;

output T10P[3]; T10P=state;

output T11P[4]; T11P=point;

output T12P; T12P=chg;

output T13P; T13P=swap01p;

output T14P; T14P=swap12p;

output T15P; T15P=swap23p;

output T16P; T16P=swap34p;

output T17P; T17P=swap45p;

output T18P; T18P=swap56p;

output T19P; T19P=swap67p;

output T20P; T20P=swap78p;

output T21P; T21P=swap89p;

output T22P[8]; T22P=dataout;

eos=hit.1;

enable(data,datain,dataout,datacnt)

datacnt=we&cs;

if (reset)

memory0d=0;

else

if (cs)

if (address==0)

if (we)

memory0d=datain;

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

else

if (swap01p)

memory0d=memory1d;

else

memory0d=memory0d;

endif

endif

endif

if (reset)

memory1d=0;

else

if (cs)

if (address==1)

if (we)

memory1d=datain;

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

else

if (swap01p)

memory1d=memory0d;

else

if (swap12p)

memory1d=memory2d;

else

memory1d=memory1d;

endif

endif

endif

endif

if (reset)

memory2d=0;

else

if (cs)

if (address==2)

if (we)

memory2d=datain;

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

else

if (swap12p)

memory2d=memory1d;

else

if (swap23p)

memory2d=memory3d;

else

memory2d=memory2d;

endif

endif

endif

endif

if (reset)

memory3d=0;

else

if (cs)

if (address==3)

if (we)

memory3d=datain;

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

else

if (swap23p)

memory3d=memory2d;

else

if (swap34p)

memory3d=memory4d;

else

memory3d=memory3d;

endif

endif

endif

endif

if (reset)

memory4d=0;

else

if (cs)

if (address==4)

if (we)

memory4d=datain;

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

else

if (swap34p)

memory4d=memory3d;

else

if (swap45p)

memory4d=memory5d;

else

memory4d=memory4d;

endif

endif

endif

endif

if (reset)

memory5d=0;

else

if (cs)

if (address==5)

if (we)

memory5d=datain;

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

else

if (swap45p)

memory5d=memory4d;

else

if (swap56p)

memory5d=memory6d;

else

memory5d=memory5d;

endif

endif

endif

endif

if (reset)

memory6d=0;

else

if (cs)

if (address==6)

if (we)

memory6d=datain;

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

else

if (swap56p)

memory6d=memory5d;

else

if (swap67p)

memory6d=memory7d;

else

memory6d=memory6d;

endif

endif

endif

endif

if (reset)

memory7d=0;

else

if (cs)

if (address==7)

if (we)

memory7d=datain;

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

else

if (swap67p)

memory7d=memory6d;

else

if (swap78p)

memory7d=memory8d;

else

memory7d=memory7d;

endif

endif

endif

endif

if (reset)

memory8d=0;

else

if (cs)

if (address==8)

if (we)

memory8d=datain;

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

else

if (swap78p)

memory8d=memory7d;

else

if (swap89p)

memory8d=memory9d;

else

memory8d=memory8d;

endif

endif

endif

endif

if (reset)

memory9d=0;

else

if (cs)

if (address==9)

if (we)

memory9d=datain;

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

else

if (swap89p)

memory9d=memory8d;

else

memory9d=memory9d;

endif

endif

endif

switch(address)

case 0: dataout=memory0d;

case 1: dataout=memory1d;

case 2: dataout=memory2d;

case 3: dataout=memory3d;

case 4: dataout=memory4d;

case 5: dataout=memory5d;

case 6: dataout=memory6d;

case 7: dataout=memory7d;

case 8: dataout=memory8d;

case 9: dataout=memory9d;

endswitch

if (reset)

state=0;

else

if (exec)

if (stateend)

state=0;

else

state=state+1;

endif

else

state=0;

endif

endif

if (reset)

point=0;

else

if (stateend)

if (point==8)

point=0;

else

point=point+1;

endif

else

point=point;

endif

endif

if (exec)

switch(state)

case 0: state0p=1;

case 1: state1p=1;

stateend=1;

endswitch

endif

switch(point)

case 0:

if (state0p)

if (memory0d>memory1d) chg=1; endif

else

chg=chg;

endif

case 1:

if (state0p)

if (memory1d>memory2d) chg=1; endif

else

chg=chg;

endif

case 2:

if (state0p)

if (memory2d>memory3d) chg=1; endif

else

chg=chg;

endif

case 3:

if (state0p)

if (memory3d>memory4d) chg=1; endif

else

chg=chg;

endif

case 4:

if (state0p)

if (memory4d>memory5d) chg=1; endif

else

chg=chg;

endif

case 5:

if (state0p)

if (memory5d>memory6d) chg=1; endif

else

chg=chg;

endif

case 6:

if (state0p)

if (memory6d>memory7d) chg=1; endif

else

chg=chg;

endif

case 7:

if (state0p)

if (memory7d>memory8d) chg=1; endif

else

chg=chg;

endif

case 8:

if (state0p)

if (memory8d>memory9d) chg=1; endif

else

chg=chg;

endif

endswitch

if (state1p)

switch(point)

case 0: if (chg) swap01p=1; endif

case 1: if (chg) swap12p=1; endif

case 2: if (chg) swap23p=1; endif

case 3: if (chg) swap34p=1; endif

case 4: if (chg) swap45p=1; endif

case 5: if (chg) swap56p=1; endif

case 6: if (chg) swap67p=1; endif

case 7: if (chg) swap78p=1; endif

case 8: if (chg) swap89p=1; endif

endswitch

endif

if (reset)

hit=0;

else

if (exec)

if ((state==1)&(point==8))

switch(hit)

case 0: hit=2;

case 1: hit=0;

case 2: hit=hit;

endswitch

else

if (chg)

hit=1;

else

hit=hit;

endif

endif

else

hit=0;

endif

endif

ende

entity sim

output reset;

output cs;

output re;

output we;

output exec;

output address[4];

output data[8];

output eos;

bitr tc[10];

part main(reset,cs,re,we,exec,address,data,eos)

tc=tc+1;

if (tc<5) reset=1; endif

switch(tc)

case 7: cs=1; we=1; data=10; address=0;

case 8: cs=1; we=1; data=9 ; address=1;

case 9: cs=1; we=1; data=8 ; address=2;

case 10: cs=1; we=1; data=7 ; address=3;

case 11: cs=1; we=1; data=6 ; address=4;

case 12: cs=1; we=1; data=5 ; address=5;

case 13: cs=1; we=1; data=4 ; address=6;

case 14: cs=1; we=1; data=3 ; address=7;

case 15: cs=1; we=1; data=2 ; address=8;

case 16: cs=1; we=1; data=1 ; address=9;

endswitch

if (tc>20) exec=1; endif

switch(tc)

case 205: cs=1; re=1; address=0;

case 206: cs=1; re=1; address=1;

case 207: cs=1; re=1; address=2;

case 208: cs=1; re=1; address=3;

case 209: cs=1; re=1; address=4;

case 210: cs=1; re=1; address=5;

case 211: cs=1; re=1; address=6;

case 212: cs=1; re=1; address=7;

case 213: cs=1; re=1; address=8;

case 214: cs=1; re=1; address=9;

endswitch

ende

endlogic

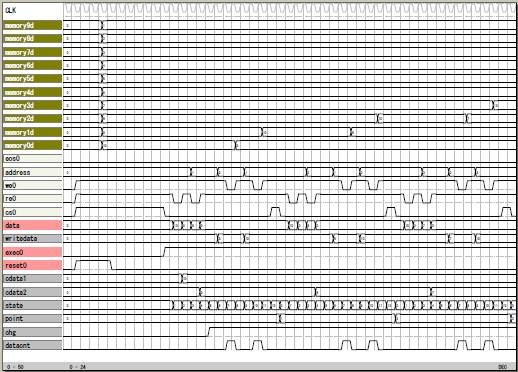

その2

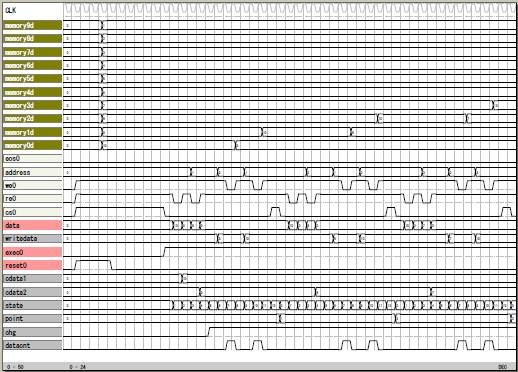

外部のメモリにあるデータを小さい順番に並び替えます。

file: sample25

論理譜

logicname yahoo34

entity main

input reset;

input exec;

inout data[8];

output cs;

output re;

output we;

output address[4];

output eos;

output writedata[8];

bitn datain[8];

bitn dataout[8];

bitn datacnt;

bitr state[4];

bitn stateend;

bitr point[4];

bitn state0p;

bitn state1p;

bitn state2p;

bitn state3p;

bitn state4p;

bitn state5p;

bitn state6p;

bitn state7p;

bitn state8p;

bitn state9p;

bitn state10p;

bitn state11p;

bitn nwe;

bitn nre;

bitn ncs;

bitr cdata1[8];

bitr cdata2[8];

bitr chg;

bitr naddress[4];

bitr ndata[8];

bitr hit[2];

output T0P[8]; T0P=cdata1;

output T1P[8]; T1P=cdata2;

output T2P[4]; T2P=state;

output T3P[4]; T3P=point;

output T4P; T4P=chg;

output T5P; T5P=datacnt;

enable(data,datain,dataout,datacnt)

datacnt=ncs&nwe;

dataout=ndata;

we=!nwe;

re=!nre;

cs=!ncs;

address=naddress;

writedata=ndata;

eos=hit.1;

if (reset)

state=0;

else

if (exec)

if (stateend)

state=0;

else

state=state+1;

endif

else

state=0;

endif

endif

if (reset)

point=0;

else

if (exec)

if (stateend)

if (point==8)

point=0;

else

point=point+1;

endif

else

point=point;

endif

else

point=0;

endif

endif

if (exec)

switch(state)

case 0: state0p=1;

case 1: state1p=1; { メモリ読み出し1 }

case 2: state2p=1;

case 3: state3p=1; { メモリ読み出し2 }

case 4: state4p=1;

case 5: state5p=1; { データ比較 }

case 6: state6p=1;

case 7: state7p=1; { メモリ書き込み1 }

case 8: state8p=1;

case 9: state9p=1;

case 10: state10p=1; { メモリ書き込み2 }

case 11: state11p=1;

case 12: stateend=1;

endswitch

endif

if (state0p) ncs=1; endif

if (state1p) ncs=1; nre=1; endif

if (state2p) ncs=1; endif

if (state3p) ncs=1; nre=1; endif

if (state4p) ncs=1; endif

if (state5p) ncs=1; endif

if (state6p) ncs=1; endif

if (state7p) ncs=1; nwe=1; endif

if (state8p) ncs=1; endif

if (state9p) ncs=1; endif

if (state10p) ncs=1; nwe=1; endif

if (state11p) ncs=1; endif

if (reset)

naddress=0;

else

if (state5p|state0p)

switch(point)

case 0: naddress=0;

case 1: naddress=1;

case 2: naddress=2;

case 3: naddress=3;

case 4: naddress=4;

case 5: naddress=5;

case 6: naddress=6;

case 7: naddress=7;

case 8: naddress=8;

endswitch

else

if (state8p|state2p)

switch(point)

case 0: naddress=1;

case 1: naddress=2;

case 2: naddress=3;

case 3: naddress=4;

case 4: naddress=5;

case 5: naddress=6;

case 6: naddress=7;

case 7: naddress=8;

case 8: naddress=9;

endswitch

else

naddress=naddress;

endif

endif

endif

if (reset)

ndata=0;

else

if (state5p)

if (chg)

ndata=cdata2;

else

ndata=cdata1;

endif

else

if (state8p)

if (chg)

ndata=cdata1;

else

ndata=cdata2;

endif

else

ndata=ndata;

endif

endif

endif

if (reset)

cdata1=0;

else

if (state1p)

cdata1=datain;

else

cdata1=cdata1;

endif

endif

if (reset)

cdata2=0;

else

if (state3p)

cdata2=datain;

else

cdata2=cdata2;

endif

endif

if (reset)

chg=0;

else

if (state4p)

if (cdata1>cdata2)

chg=1;

else

chg=0;

endif

else

chg=chg;

endif

endif

if (reset)

hit=0;

else

if (exec)

if ((stateend)&(point==8))

switch(hit)

case 0: hit=2;

case 1: hit=0;

case 2: hit=hit;

endswitch

else

if (chg)

hit=1;

else

hit=hit;

endif

endif

else

hit=0;

endif

endif

ende

entity sim

output reset;

output exec;

output data[8];

output cs;

output re;

output we;

output address[4];

output eos;

output writedata[8];

output TB0P[8];

output TB1P[8];

output TB2P[8];

output TB3P[8];

output TB4P[8];

output TB5P[8];

output TB6P[8];

output TB7P[8];

output TB8P[8];

output TB9P[8];

bitr memory0d[8];

bitr memory1d[8];

bitr memory2d[8];

bitr memory3d[8];

bitr memory4d[8];

bitr memory5d[8];

bitr memory6d[8];

bitr memory7d[8];

bitr memory8d[8];

bitr memory9d[8];

bitn node_cs;

bitn node_re;

bitn node_we;

bitn node_address[4];

bitn node_writedata[8];

bitr tc[11];

bitn memini;

TB0P=memory0d;

TB1P=memory1d;

TB2P=memory2d;

TB3P=memory3d;

TB4P=memory4d;

TB5P=memory5d;

TB6P=memory6d;

TB7P=memory7d;

TB8P=memory8d;

TB9P=memory9d;

cs=node_cs;

re=node_re;

we=node_we;

address=node_address;

writedata=node_writedata;

part main(reset,exec,data,node_cs,node_re,node_we,node_address,eos,node_writedata)

tc=tc+1;

if (tc<5) reset=1; endif

if (tc==3) memini=1; endif

if (tc>10) exec=1; endif

if (memini)

memory0d=10;

else

if (!node_cs)

if (!node_we)

if (node_address==0)

memory0d=node_writedata;

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

endif

if (memini)

memory1d=9;

else

if (!node_cs)

if (!node_we)

if (node_address==1)

memory1d=node_writedata;

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

endif

if (memini)

memory2d=8;

else

if (!node_cs)

if (!node_we)

if (node_address==2)

memory2d=node_writedata;

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

endif

if (memini)

memory3d=7;

else

if (!node_cs)

if (!node_we)

if (node_address==3)

memory3d=node_writedata;

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

endif

if (memini)

memory4d=6;

else

if (!node_cs)

if (!node_we)

if (node_address==4)

memory4d=node_writedata;

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

endif

if (memini)

memory5d=5;

else

if (!node_cs)

if (!node_we)

if (node_address==5)

memory5d=node_writedata;

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

endif

if (memini)

memory6d=4;

else

if (!node_cs)

if (!node_we)

if (node_address==6)

memory6d=node_writedata;

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

endif

if (memini)

memory7d=3;

else

if (!node_cs)

if (!node_we)

if (node_address==7)

memory7d=node_writedata;

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

endif

if (memini)

memory8d=2;

else

if (!node_cs)

if (!node_we)

if (node_address==8)

memory8d=node_writedata;

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

endif

if (memini)

memory9d=1;

else

if (!node_cs)

if (!node_we)

if (node_address==9)

memory9d=node_writedata;

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

endif

if (!node_cs&!node_re)

switch(node_address)

case 0: data=memory0d;

case 1: data=memory1d;

case 2: data=memory2d;

case 3: data=memory3d;

case 4: data=memory4d;

case 5: data=memory5d;

case 6: data=memory6d;

case 7: data=memory7d;

case 8: data=memory8d;

case 9: data=memory9d;

endswitch

endif

ende

endlogic

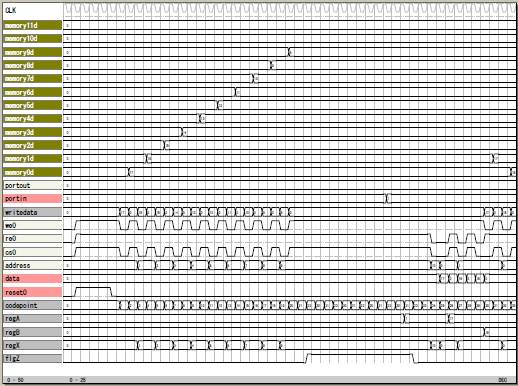

その3

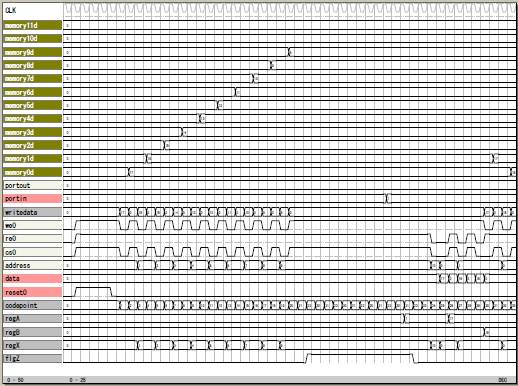

小さな8ビットプロセッサを作って並び替えます。

プロセッサのプログラムはチップに内蔵します。

file: sample26

論理譜

logicname yahoo36

entity main

input reset;

input portin[8];

inout data[8];

output address[4];

output cs;

output re;

output we;

output portout[8];

output writedata[8];

bitn datain[8];

bitn dataout[8];

bitn datacnt;

bitr codepoint[8];

bitn codec[5];

bitn coded[8];

bitr regA[8];

bitr regB[8];

bitr regX[8];

bitr flgC;

bitr flgZ;

bitr regport[8];

bitn codec1p;

bitn codec2p;

bitn codec3p;

bitn codec4p;

bitn codec5p;

bitn codec6p;

bitn codec7p;

bitn codec8p;

bitn codec9p;

bitn codec10p;

bitn codec11p;

bitn codec12p;

bitn codec13p;

bitn codec14p;

bitn codec15p;

bitn codec16p;

bitn codec17p;

bitn codec18p;

bitn codec19p;

bitn codec20p;

bitn codec21p;

bitn codec22p;

bitn codec23p;

bitn codec24p;

bitn codec25p;

bitn codec26p;

bitn codec27p;

bitn codec28p;

bitn codec29p;

bitn codec30p;

bitn calcy[9];

bitn calca[9];

bitn calcb[9];

output T0P[8]; T0P=codepoint;

output T1P[8]; T1P=regB;

output T2P[8]; T2P=regA;

output T3P[8]; T3P=regX;

output T4P; T4P=flgZ;

address=regX.0:3;

writedata=dataout;

we=!datacnt;

re=!(codec2p|codec5p|codec27p|codec28p);

cs=!(codec1p|codec2p|codec5p|codec23p|codec26p|codec27p|codec28p);

portout=regport;

enable(data,datain,dataout,datacnt)

datain.8=1;

switch(codec)

case 1: dataout=regA;

case 23: dataout=coded;

case 26: dataout=regB;

endswitch

if (codec1p|codec23p|codec26p) datacnt=1; endif

if (reset)

codepoint=0;

else

if (codec6p&flgC)

codepoint=coded;

else

if (codec7p&!flgC)

codepoint=coded;

else

if (codec8p&flgZ)

codepoint=coded;

else

if (codec9p&!flgZ)

codepoint=coded;

else

if (codec10p)

codepoint=coded;

else

codepoint=codepoint+1;

endif

endif

endif

endif

endif

endif

switch(codepoint)

case 0: codec=0; coded=0;

case 1: codec=23; coded=17; { LD (X),17 }

case 2: codec=4; coded=1; { LD X,1 }

case 3: codec=23; coded=16; { LD (X),16 }

case 4: codec=4; coded=2; { LD X,2 }

case 5: codec=23; coded=15; { LD (X),15 }

case 6: codec=4; coded=3; { LD X,3 }

case 7: codec=23; coded=14; { LD (X),14 }

case 8: codec=4; coded=4; { LD X,4 }

case 9: codec=23; coded=13; { LD (X),13 }

case 10: codec=4; coded=5; { LD X,5 }

case 11: codec=23; coded=12; { LD (X),12 }

case 12: codec=4; coded=6; { LD X,6 }

case 13: codec=23; coded=11; { LD (X),11 }

case 14: codec=4; coded=7; { LD X,7 }

case 15: codec=23; coded=10; { LD (X),10 }

case 16: codec=4; coded=8; { LD X,8 }

case 17: codec=23; coded=9; { LD (X),9 }

case 18: codec=4; coded=9; { LD X,9 }

case 19: codec=23; coded=8; { LD (X),8 }

case 20: codec=29; { LD A,PORT }

case 21: codec=13; coded=0; { CMP A,0 }

case 22: codec=8; coded=20; { JPZ 20 }

case 23: codec=4; coded=10; { LD X,10 }

case 24: codec=28; { LD X,(X) }

case 25: codec=2; { LD A,(X) }

case 26: codec=15; { INC X }

case 27: codec=5; { CMP A,(X) }

case 28: codec=6; coded=49; { JPC 49 }

case 29: codec=27; { LD B,(X) }

case 30: codec=1; { LD (X),A }

case 31: codec=25; { DEC X }

case 32: codec=26; { LD (X),B }

case 33: codec=22; { LD A,X }

case 34: codec=4; coded=11; { LD X,11 }

case 35: codec=23; coded=255; { LD (X),0FFh }

case 36: codec=21; { LD X,A }

case 37: codec=10; coded=49; { JP 49 }

case 49: codec=15; { INC X }

case 50: codec=22; { LD A,X }

case 51: codec=13; coded=9; { CMP A,9 }

case 52: codec=6; coded=60; { JPC 60 }

case 53: codec=4; coded=11; { LD X,11 }

case 54: codec=3; coded=0; { LD A,0 }

case 55: codec=5; { CMP A,(X) }

case 56: codec=8; coded=70; { JPZ 70 }

case 57: codec=23; coded=0; { LD (X),0 }

case 58: codec=3; coded=0; { LD A,0 }

case 60: codec=4; coded=10; { LD X,10 }

case 61: codec=1; { LD (X),A }

case 62: codec=10; coded=23; { JP 23 }

case 70: codec=3; coded=1; { LD A,1 }

case 71: codec=30; { LD PORT,A }

case 72: codec=10; coded=72; { JP 72 }

endswitch

if (reset)

regport=0;

else

if (codec30p)

regport=regA;

else

regport=regport;

endif

endif

if (reset)

regA=0;

else

switch(codec)

case 2: regA=datain;

case 3: regA=coded;

case 14: regA=regA+1;

case 20: regA=regB;

case 22: regA=regX;

case 24: regA=regA-1;

case 29: regA=portin;

default: regA=regA;

endswitch

endif

if (reset)

regB=0;

else

switch(codec)

case 11: regB=regA;

case 27: regB=datain;

default: regB=regB;

endswitch

endif

if (reset)

regX=0;

else

switch(codec)

case 4: regX=coded;

case 15: regX=regX+1;

case 21: regX=regA;

case 25: regX=regX-1;

case 28: regX=datain;

default: regX=regX;

endswitch

endif

if (reset)

flgC=0;

else

if (codec5p)

if (regA<datain)

flgC=1;

else

flgC=0;

endif

else

if (codec12p)

if (regA<regB)

flgC=1;

else

flgC=0;

endif

else

if (codec13p)

if (regA<coded)

flgC=1;

else

flgC=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.8)

flgC=1;

else

flgC=0;

endif

else

flgC=flgC;

endif

endif

endif

endif

endif

if (reset)

flgZ=0;

else

if (codec5p)

if (regA==datain)

flgZ=1;

else

flgZ=0;

endif

else

if (codec12p)

if (regA==regB)

flgZ=1;

else

flgZ=0;

endif

else

if (codec13p)

if (regA==coded)

flgZ=1;

else

flgZ=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.0:7==0)

flgZ=1;

else

flgZ=0;

endif

else

flgZ=flgZ;

endif

endif

endif

endif

endif

calca.0:7=regA;

switch(codec)

case 16: calcb.0:7=regB;

case 17: calcb.0:7=coded;

case 18: calcb.0:7=regB;

case 19: calcb.0:7=coded;

endswitch

if (codec16p|codec17p) calcy=calca+calcb; endif

if (codec18p|codec19p) calcy=calca-calcb; endif

switch(codec)

case 1: codec1p=1;

case 2: codec2p=1;

case 3: codec3p=1;

case 4: codec4p=1;

case 5: codec5p=1;

case 6: codec6p=1;

case 7: codec7p=1;

case 8: codec8p=1;

case 9: codec9p=1;

case 10: codec10p=1;

case 11: codec11p=1;

case 12: codec12p=1;

case 13: codec13p=1;

case 14: codec14p=1;

case 15: codec15p=1;

case 16: codec16p=1;

case 17: codec17p=1;

case 18: codec18p=1;

case 19: codec19p=1;

case 20: codec20p=1;

case 21: codec21p=1;

case 22: codec22p=1;

case 23: codec23p=1;

case 24: codec24p=1;

case 25: codec25p=1;

case 26: codec26p=1;

case 27: codec27p=1;

case 28: codec28p=1;

case 29: codec29p=1;

case 30: codec30p=1;

endswitch

ende

entity sim

output reset;

output portin[8];

output data[8];

output address[4];

output cs;

output re;

output we;

output portout[8];

output writedata[8];

output TB0P[8];

output TB1P[8];

output TB2P[8];

output TB3P[8];

output TB4P[8];

output TB5P[8];

output TB6P[8];

output TB7P[8];

output TB8P[8];

output TB9P[8];

output TB10P[8];

output TB11P[8];

bitr tc[11];

bitr memory0d[8];

bitr memory1d[8];

bitr memory2d[8];

bitr memory3d[8];

bitr memory4d[8];

bitr memory5d[8];

bitr memory6d[8];

bitr memory7d[8];

bitr memory8d[8];

bitr memory9d[8];

bitr memory10d[8];

bitr memory11d[8];

bitn node_reset;

bitn node_cs;

bitn node_re;

bitn node_we;

bitn node_address[4];

bitn node_writedata[8];

TB0P=memory0d;

TB1P=memory1d;

TB2P=memory2d;

TB3P=memory3d;

TB4P=memory4d;

TB5P=memory5d;

TB6P=memory6d;

TB7P=memory7d;

TB8P=memory8d;

TB9P=memory9d;

TB10P=memory10d;

TB11P=memory11d;

reset=node_reset;

cs=node_cs;

re=node_re;

we=node_we;

address=node_address;

writedata=node_writedata;

part main(node_reset,portin,data,node_address,node_cs,node_re,node_we,portout,node_writedata)

tc=tc+1;

if (tc<5) node_reset=1; endif

if (tc>35) portin=1; endif

if (node_reset)

memory0d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==0)

memory0d=node_writedata;

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

endif

if (node_reset)

memory1d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==1)

memory1d=node_writedata;

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

endif

if (node_reset)

memory2d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==2)

memory2d=node_writedata;

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

endif

if (node_reset)

memory3d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==3)

memory3d=node_writedata;

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

endif

if (node_reset)

memory4d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==4)

memory4d=node_writedata;

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

endif

if (node_reset)

memory5d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==5)

memory5d=node_writedata;

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

endif

if (node_reset)

memory6d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==6)

memory6d=node_writedata;

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

endif

if (node_reset)

memory7d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==7)

memory7d=node_writedata;

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

endif

if (node_reset)

memory8d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==8)

memory8d=node_writedata;

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

endif

if (node_reset)

memory9d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==9)

memory9d=node_writedata;

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

endif

if (node_reset)

memory10d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==10)

memory10d=node_writedata;

else

memory10d=memory10d;

endif

else

memory10d=memory10d;

endif

else

memory10d=memory10d;

endif

endif

if (node_reset)

memory11d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==11)

memory11d=node_writedata;

else

memory11d=memory11d;

endif

else

memory11d=memory11d;

endif

else

memory11d=memory11d;

endif

endif

if (!node_cs&!node_re)

switch(node_address)

case 0: data=memory0d;

case 1: data=memory1d;

case 2: data=memory2d;

case 3: data=memory3d;

case 4: data=memory4d;

case 5: data=memory5d;

case 6: data=memory6d;

case 7: data=memory7d;

case 8: data=memory8d;

case 9: data=memory9d;

case 10: data=memory10d;

case 11: data=memory11d;

endswitch

endif

ende

endlogic

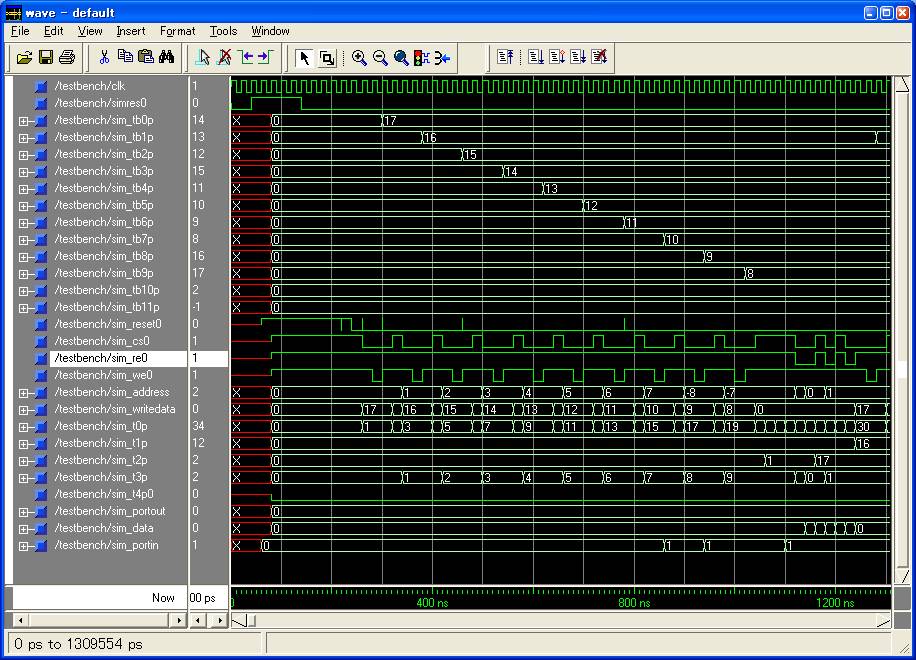

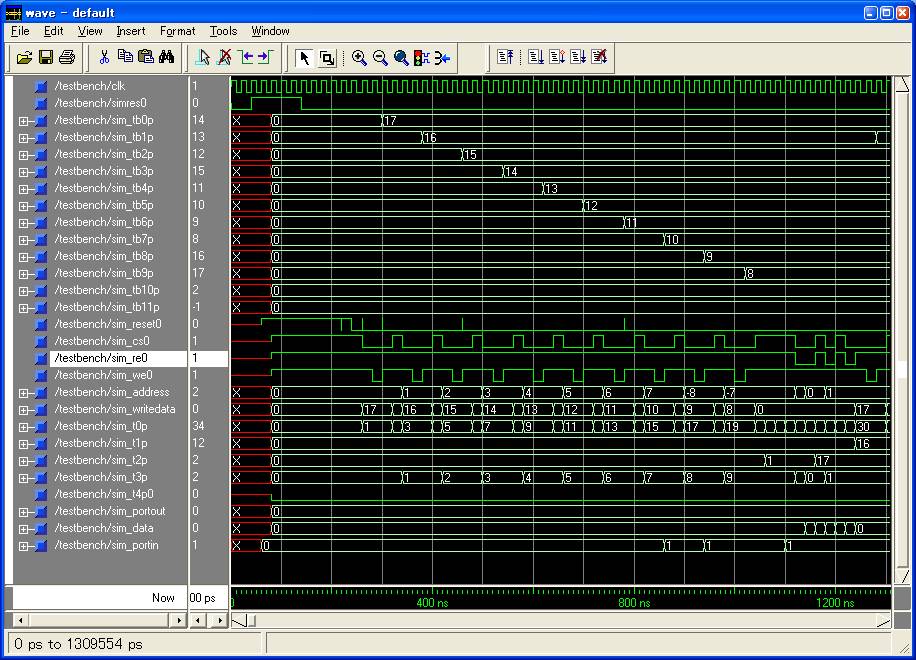

その4

並び替え用の8ビットプロセッサの書き込み信号を非同

期のメモリに適合するように修正してModelSimで実行

させてみました。

ldc y37 -vh -opt 0 -qm 0 -floop 1 -sp 3000 -bundle

で e1.vhd が論理式ファイルで s1.vhd がテストベンチに

なります。

file: sample27

論理譜

logicname yahoo37

entity main

input reset;

input portin[8];

inout data[8];

output address[4];

output cs;

output re;

output we;

output portout[8];

output writedata[8];

bitn datain[8];

bitn dataout[8];

bitn datacnt;

bitr codepoint[8];

bitn codec[5];

bitn coded[8];

bitr regA[8];

bitr regB[8];

bitr regX[8];

bitr flgC;

bitr flgZ;

bitr regport[8];

bitn codec1p;

bitn codec2p;

bitn codec3p;

bitn codec4p;

bitn codec5p;

bitn codec6p;

bitn codec7p;

bitn codec8p;

bitn codec9p;

bitn codec10p;

bitn codec11p;

bitn codec12p;

bitn codec13p;

bitn codec14p;

bitn codec15p;

bitn codec16p;

bitn codec17p;

bitn codec18p;

bitn codec19p;

bitn codec20p;

bitn codec21p;

bitn codec22p;

bitn codec23p;

bitn codec24p;

bitn codec25p;

bitn codec26p;

bitn codec27p;

bitn codec28p;

bitn codec29p;

bitn codec30p;

bitn calcy[9];

bitn calca[9];

bitn calcb[9];

bitr wseq[2];

output T0P[8]; T0P=codepoint;

output T1P[8]; T1P=regB;

output T2P[8]; T2P=regA;

output T3P[8]; T3P=regX;

output T4P; T4P=flgZ;

address=regX.0:3;

writedata=dataout;

we=!(datacnt&(wseq==1)); { 非同期メモリ用に修正 }

re=!(codec2p|codec5p|codec27p|codec28p);

cs=!(codec1p|codec2p|codec5p|codec23p|codec26p|codec27p|codec28p);

portout=regport;

enable(data,datain,dataout,datacnt)

datain.8=1;

switch(codec)

case 1: dataout=regA;

case 23: dataout=coded;

case 26: dataout=regB;

endswitch

if (codec1p|codec23p|codec26p) datacnt=1; endif

if (reset) { ----------}

wseq=0; { }

else { 非同期 }

if (datacnt) { メモリ用 }

wseq=wseq+1; { に追加 }

else { }

wseq=0; { }

endif { }

endif { --------- }

if (reset)

codepoint=0;

else

if (codec6p&flgC)

codepoint=coded;

else

if (codec7p&!flgC)

codepoint=coded;

else

if (codec8p&flgZ)

codepoint=coded;

else

if (codec9p&!flgZ)

codepoint=coded;

else

if (codec10p)

codepoint=coded;

else

if (datacnt) { --------- }

if (wseq==2) { }

codepoint=codepoint+1; { 非同期 }

else { メモリ用 }

codepoint=codepoint; { に追加 }

endif { }

else { --------- }

codepoint=codepoint+1;

endif

endif

endif

endif

endif

endif

endif

switch(codepoint)

case 0: codec=0; coded=0;

case 1: codec=23; coded=17; { LD (X),17 }

case 2: codec=4; coded=1; { LD X,1 }

case 3: codec=23; coded=16; { LD (X),16 }

case 4: codec=4; coded=2; { LD X,2 }

case 5: codec=23; coded=15; { LD (X),15 }

case 6: codec=4; coded=3; { LD X,3 }

case 7: codec=23; coded=14; { LD (X),14 }

case 8: codec=4; coded=4; { LD X,4 }

case 9: codec=23; coded=13; { LD (X),13 }

case 10: codec=4; coded=5; { LD X,5 }

case 11: codec=23; coded=12; { LD (X),12 }

case 12: codec=4; coded=6; { LD X,6 }

case 13: codec=23; coded=11; { LD (X),11 }

case 14: codec=4; coded=7; { LD X,7 }

case 15: codec=23; coded=10; { LD (X),10 }

case 16: codec=4; coded=8; { LD X,8 }

case 17: codec=23; coded=9; { LD (X),9 }

case 18: codec=4; coded=9; { LD X,9 }

case 19: codec=23; coded=8; { LD (X),8 }

case 20: codec=29; { LD A,PORT }

case 21: codec=13; coded=0; { CMP A,0 }

case 22: codec=8; coded=20; { JPZ 20 }

case 23: codec=4; coded=10; { LD X,10 }

case 24: codec=28; { LD X,(X) }

case 25: codec=2; { LD A,(X) }

case 26: codec=15; { INC X }

case 27: codec=5; { CMP A,(X) }

case 28: codec=6; coded=49; { JPC 49 }

case 29: codec=27; { LD B,(X) }

case 30: codec=1; { LD (X),A }

case 31: codec=25; { DEC X }

case 32: codec=26; { LD (X),B }

case 33: codec=22; { LD A,X }

case 34: codec=4; coded=11; { LD X,11 }

case 35: codec=23; coded=255; { LD (X),0FFh }

case 36: codec=21; { LD X,A }

case 37: codec=10; coded=49; { JP 49 }

case 49: codec=15; { INC X }

case 50: codec=22; { LD A,X }

case 51: codec=13; coded=9; { CMP A,9 }

case 52: codec=6; coded=60; { JPC 60 }

case 53: codec=4; coded=11; { LD X,11 }

case 54: codec=3; coded=0; { LD A,0 }

case 55: codec=5; { CMP A,(X) }

case 56: codec=8; coded=70; { JPZ 70 }

case 57: codec=23; coded=0; { LD (X),0 }

case 58: codec=3; coded=0; { LD A,0 }

case 60: codec=4; coded=10; { LD X,10 }

case 61: codec=1; { LD (X),A }

case 62: codec=10; coded=23; { JP 23 }

case 70: codec=3; coded=1; { LD A,1 }

case 71: codec=30; { LD PORT,A }

case 72: codec=10; coded=72; { JP 72 }

endswitch

if (reset)

regport=0;

else

if (codec30p)

regport=regA;

else

regport=regport;

endif

endif

if (reset)

regA=0;

else

switch(codec)

case 2: regA=datain;

case 3: regA=coded;

case 14: regA=regA+1;

case 20: regA=regB;

case 22: regA=regX;

case 24: regA=regA-1;

case 29: regA=portin;

default: regA=regA;

endswitch

endif

if (reset)

regB=0;

else

switch(codec)

case 11: regB=regA;

case 27: regB=datain;

default: regB=regB;

endswitch

endif

if (reset)

regX=0;

else

switch(codec)

case 4: regX=coded;

case 15: regX=regX+1;

case 21: regX=regA;

case 25: regX=regX-1;

case 28: regX=datain;

default: regX=regX;

endswitch

endif

if (reset)

flgC=0;

else

if (codec5p)

if (regA<datain)

flgC=1;

else

flgC=0;

endif

else

if (codec12p)

if (regA<regB)

flgC=1;

else

flgC=0;

endif

else

if (codec13p)

if (regA<coded)

flgC=1;

else

flgC=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.8)

flgC=1;

else

flgC=0;

endif

else

flgC=flgC;

endif

endif

endif

endif

endif

if (reset)

flgZ=0;

else

if (codec5p)

if (regA==datain)

flgZ=1;

else

flgZ=0;

endif

else

if (codec12p)

if (regA==regB)

flgZ=1;

else

flgZ=0;

endif

else

if (codec13p)

if (regA==coded)

flgZ=1;

else

flgZ=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.0:7==0)

flgZ=1;

else

flgZ=0;

endif

else

flgZ=flgZ;

endif

endif

endif

endif

endif

calca.0:7=regA;

switch(codec)

case 16: calcb.0:7=regB;

case 17: calcb.0:7=coded;

case 18: calcb.0:7=regB;

case 19: calcb.0:7=coded;

endswitch

if (codec16p|codec17p) calcy=calca+calcb; endif

if (codec18p|codec19p) calcy=calca-calcb; endif

switch(codec)

case 1: codec1p=1;

case 2: codec2p=1;

case 3: codec3p=1;

case 4: codec4p=1;

case 5: codec5p=1;

case 6: codec6p=1;

case 7: codec7p=1;

case 8: codec8p=1;

case 9: codec9p=1;

case 10: codec10p=1;

case 11: codec11p=1;

case 12: codec12p=1;

case 13: codec13p=1;

case 14: codec14p=1;

case 15: codec15p=1;

case 16: codec16p=1;

case 17: codec17p=1;

case 18: codec18p=1;

case 19: codec19p=1;

case 20: codec20p=1;

case 21: codec21p=1;

case 22: codec22p=1;

case 23: codec23p=1;

case 24: codec24p=1;

case 25: codec25p=1;

case 26: codec26p=1;

case 27: codec27p=1;

case 28: codec28p=1;

case 29: codec29p=1;

case 30: codec30p=1;

endswitch

ende

entity sim

output reset;

output portin[8];

output data[8];

output address[4];

output cs;

output re;

output we;

output portout[8];

output writedata[8];

output TB0P[8];

output TB1P[8];

output TB2P[8];

output TB3P[8];

output TB4P[8];

output TB5P[8];

output TB6P[8];

output TB7P[8];

output TB8P[8];

output TB9P[8];

output TB10P[8];

output TB11P[8];

input simres; { ModlSim 用に追加 }

bitr tc[12];

bitr memory0d[8];

bitr memory1d[8];

bitr memory2d[8];

bitr memory3d[8];

bitr memory4d[8];

bitr memory5d[8];

bitr memory6d[8];

bitr memory7d[8];

bitr memory8d[8];

bitr memory9d[8];

bitr memory10d[8];

bitr memory11d[8];

bitn node_reset;

bitn node_cs;

bitn node_re;

bitn node_we;

bitn node_address[4];

bitn node_writedata[8];

TB0P=memory0d;

TB1P=memory1d;

TB2P=memory2d;

TB3P=memory3d;

TB4P=memory4d;

TB5P=memory5d;

TB6P=memory6d;

TB7P=memory7d;

TB8P=memory8d;

TB9P=memory9d;

TB10P=memory10d;

TB11P=memory11d;

reset=node_reset;

cs=node_cs;

re=node_re;

we=node_we;

address=node_address;

writedata=node_writedata;

part main(node_reset,portin,data,node_address,node_cs,node_re,node_we,portout,node_writedata)

if (!simres) tc=tc+1; endif { ModelSim 用に修正 }

if (tc<5) node_reset=1; endif

if (tc>35) portin=1; endif

if (node_reset)

memory0d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==0)

memory0d=node_writedata;

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

endif

if (node_reset)

memory1d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==1)

memory1d=node_writedata;

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

endif

if (node_reset)

memory2d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==2)

memory2d=node_writedata;

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

endif

if (node_reset)

memory3d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==3)

memory3d=node_writedata;

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

endif

if (node_reset)

memory4d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==4)

memory4d=node_writedata;

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

endif

if (node_reset)

memory5d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==5)

memory5d=node_writedata;

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

endif

if (node_reset)

memory6d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==6)

memory6d=node_writedata;

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

endif

if (node_reset)

memory7d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==7)

memory7d=node_writedata;

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

endif

if (node_reset)

memory8d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==8)

memory8d=node_writedata;

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

endif

if (node_reset)

memory9d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==9)

memory9d=node_writedata;

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

endif

if (node_reset)

memory10d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==10)

memory10d=node_writedata;

else

memory10d=memory10d;

endif

else

memory10d=memory10d;

endif

else

memory10d=memory10d;

endif

endif

if (node_reset)

memory11d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==11)

memory11d=node_writedata;

else

memory11d=memory11d;

endif

else

memory11d=memory11d;

endif

else

memory11d=memory11d;

endif

endif

if (!node_cs&!node_re)

switch(node_address)

case 0: data=memory0d;

case 1: data=memory1d;

case 2: data=memory2d;

case 3: data=memory3d;

case 4: data=memory4d;

case 5: data=memory5d;

case 6: data=memory6d;

case 7: data=memory7d;

case 8: data=memory8d;

case 9: data=memory9d;

case 10: data=memory10d;

case 11: data=memory11d;

endswitch

endif

ende

endlogic