小プロセッサ

その1

8ビットプロセッサで命令は2バイトの固定です。n は2バイト

目の値を示します。 n を使わない命令の2バイト目は0になり

ます。

レジスタ構成は

- 主レジスタ A

- 補助レジスタ B

- 番地レジスタ X

の3個のレジスタです。

命令セットは次のようにしました。

- LD (X),A

- LD A,(X)

- LD A,n

- LD X,n

- CMP A,(X)

- JPC n

- JPNC n

- JPZ n

- JPNZ n

- JP n

- LD B,A

- CMP A,B

- CMP A,n

- INC A

- INC X

- ADD A,B

- ADD A,n

- SUB A,B

- SUB A,n

- LD A,B

- LD X,A

- LD A,X

- LD (X),n

- DEC A

- DEC X

- LD (X),B

- LD B,(X)

- LD X,(X)

- LD A,PORT

- LD PORT,A

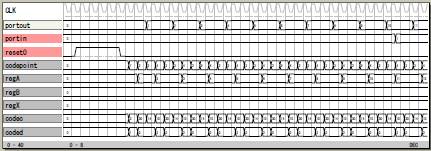

命令は1CLKで動作しますが外部のメモリが非同期の場合は書き

込み命令のみ3CLKにします。

論理譜に注釈を入れて整理しました。

論理譜

logicname yahoo38

{ ================================================================== }

{ 実効譜 }

{ ================================================================== }

entity main

{ ------------------------------------------------------------------ }

{ 入力端子 }

{ ------------------------------------------------------------------ }

input reset;

input portin[8];

{ ------------------------------------------------------------------ }

{ 双方向端子 }

{ ------------------------------------------------------------------ }

inout data[8];

{ ------------------------------------------------------------------ }

{ 出力端子 }

{ ------------------------------------------------------------------ }

output address[4];

output cs;

output re;

output we;

output portout[8];

output writedata[8];

{ ------------------------------------------------------------------ }

{ 内部信号 }

{ ------------------------------------------------------------------ }

bitn datain[8];

bitn dataout[8];

bitn datacnt;

bitr codepoint[8];

bitn codec[5];

bitn coded[8];

bitr regA[8];

bitr regB[8];

bitr regX[8];

bitr flgC;

bitr flgZ;

bitr regport[8];

bitn codec1p;

bitn codec2p;

bitn codec3p;

bitn codec4p;

bitn codec5p;

bitn codec6p;

bitn codec7p;

bitn codec8p;

bitn codec9p;

bitn codec10p;

bitn codec11p;

bitn codec12p;

bitn codec13p;

bitn codec14p;

bitn codec15p;

bitn codec16p;

bitn codec17p;

bitn codec18p;

bitn codec19p;

bitn codec20p;

bitn codec21p;

bitn codec22p;

bitn codec23p;

bitn codec24p;

bitn codec25p;

bitn codec26p;

bitn codec27p;

bitn codec28p;

bitn codec29p;

bitn codec30p;

bitn calcy[9];

bitn calca[9];

bitn calcb[9];

bitr wseq[2];

{ ------------------------------------------------------------------ }

{ 検査端子 }

{ ------------------------------------------------------------------ }

output T0P[8]; T0P=codepoint;

output T1P[8]; T1P=regB;

output T2P[8]; T2P=regA;

output T3P[8]; T3P=regX;

output T4P; T4P=flgZ;

{ ------------------------------------------------------------------ }

{ 出力代入 }

{ ------------------------------------------------------------------ }

address=regX.0:3;

writedata=dataout;

we=!(datacnt&(wseq==1));

re=!(codec2p|codec5p|codec27p|codec28p);

cs=!(codec1p|codec2p|codec5p|codec23p|codec26p|codec27p|codec28p);

portout=regport;

{ ------------------------------------------------------------------ }

{ データバス設定 }

{ ------------------------------------------------------------------ }

enable(data,datain,dataout,datacnt)

datain.8=1;

{ ------------------------------------------------------------------ }

{ メモリデータ出力 }

{ ------------------------------------------------------------------ }

switch(codec)

case 1: dataout=regA;

case 23: dataout=coded;

case 26: dataout=regB;

endswitch

{ ------------------------------------------------------------------ }

{ メモリデータバス制御 }

{ ------------------------------------------------------------------ }

if (codec1p|codec23p|codec26p) datacnt=1; endif

{ ------------------------------------------------------------------ }

{ 書き込み進行計数 }

{ ------------------------------------------------------------------ }

if (reset)

wseq=0;

else

if (datacnt)

wseq=wseq+1;

else

wseq=0;

endif

endif

{ ------------------------------------------------------------------ }

{ 命令ポインタ }

{ ------------------------------------------------------------------ }

if (reset)

codepoint=0;

else

if (codec6p&flgC)

codepoint=coded;

else

if (codec7p&!flgC)

codepoint=coded;

else

if (codec8p&flgZ)

codepoint=coded;

else

if (codec9p&!flgZ)

codepoint=coded;

else

if (codec10p)

codepoint=coded;

else

if (datacnt)

if (wseq==2)

codepoint=codepoint+1;

else

codepoint=codepoint;

endif

else

codepoint=codepoint+1;

endif

endif

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ プログラム }

{ ------------------------------------------------------------------ }

switch(codepoint)

case 0: codec=0; coded=0;

case 1: codec=23; coded=17; { LD (X),17 }

case 2: codec=4; coded=1; { LD X,1 }

case 3: codec=23; coded=16; { LD (X),16 }

case 4: codec=4; coded=2; { LD X,2 }

case 5: codec=23; coded=15; { LD (X),15 }

case 6: codec=4; coded=3; { LD X,3 }

case 7: codec=23; coded=14; { LD (X),14 }

case 8: codec=4; coded=4; { LD X,4 }

case 9: codec=23; coded=13; { LD (X),13 }

case 10: codec=4; coded=5; { LD X,5 }

case 11: codec=23; coded=12; { LD (X),12 }

case 12: codec=4; coded=6; { LD X,6 }

case 13: codec=23; coded=11; { LD (X),11 }

case 14: codec=4; coded=7; { LD X,7 }

case 15: codec=23; coded=10; { LD (X),10 }

case 16: codec=4; coded=8; { LD X,8 }

case 17: codec=23; coded=9; { LD (X),9 }

case 18: codec=4; coded=9; { LD X,9 }

case 19: codec=23; coded=8; { LD (X),8 }

case 20: codec=29; { LD A,PORT }

case 21: codec=13; coded=0; { CMP A,0 }

case 22: codec=8; coded=20; { JPZ 20 }

case 23: codec=4; coded=10; { LD X,10 }

case 24: codec=28; { LD X,(X) }

case 25: codec=2; { LD A,(X) }

case 26: codec=15; { INC X }

case 27: codec=5; { CMP A,(X) }

case 28: codec=6; coded=49; { JPC 49 }

case 29: codec=27; { LD B,(X) }

case 30: codec=1; { LD (X),A }

case 31: codec=25; { DEC X }

case 32: codec=26; { LD (X),B }

case 33: codec=22; { LD A,X }

case 34: codec=4; coded=11; { LD X,11 }

case 35: codec=23; coded=255; { LD (X),0FFh }

case 36: codec=21; { LD X,A }

case 37: codec=10; coded=49; { JP 49 }

case 49: codec=15; { INC X }

case 50: codec=22; { LD A,X }

case 51: codec=13; coded=9; { CMP A,9 }

case 52: codec=6; coded=60; { JPC 60 }

case 53: codec=4; coded=11; { LD X,11 }

case 54: codec=3; coded=0; { LD A,0 }

case 55: codec=5; { CMP A,(X) }

case 56: codec=8; coded=70; { JPZ 70 }

case 57: codec=23; coded=0; { LD (X),0 }

case 58: codec=3; coded=0; { LD A,0 }

case 60: codec=4; coded=10; { LD X,10 }

case 61: codec=1; { LD (X),A }

case 62: codec=10; coded=23; { JP 23 }

case 70: codec=3; coded=1; { LD A,1 }

case 71: codec=30; { LD PORT,A }

case 72: codec=10; coded=72; { JP 72 }

endswitch

{ ------------------------------------------------------------------ }

{ 出力ポート }

{ ------------------------------------------------------------------ }

if (reset)

regport=0;

else

if (codec30p)

regport=regA;

else

regport=regport;

endif

endif

{ ------------------------------------------------------------------ }

{ 主レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regA=0;

else

switch(codec)

case 2: regA=datain;

case 3: regA=coded;

case 14: regA=regA+1;

case 20: regA=regB;

case 22: regA=regX;

case 24: regA=regA-1;

case 29: regA=portin;

default: regA=regA;

endswitch

endif

{ ------------------------------------------------------------------ }

{ 補助レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regB=0;

else

switch(codec)

case 11: regB=regA;

case 27: regB=datain;

default: regB=regB;

endswitch

endif

{ ------------------------------------------------------------------ }

{ 番地レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regX=0;

else

switch(codec)

case 4: regX=coded;

case 15: regX=regX+1;

case 21: regX=regA;

case 25: regX=regX-1;

case 28: regX=datain;

default: regX=regX;

endswitch

endif

{ ------------------------------------------------------------------ }

{ キャリーフラグ }

{ ------------------------------------------------------------------ }

if (reset)

flgC=0;

else

if (codec5p)

if (regA<datain)

flgC=1;

else

flgC=0;

endif

else

if (codec12p)

if (regA<regB)

flgC=1;

else

flgC=0;

endif

else

if (codec13p)

if (regA<coded)

flgC=1;

else

flgC=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.8)

flgC=1;

else

flgC=0;

endif

else

flgC=flgC;

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ ゼロフラグ }

{ ------------------------------------------------------------------ }

if (reset)

flgZ=0;

else

if (codec5p)

if (regA==datain)

flgZ=1;

else

flgZ=0;

endif

else

if (codec12p)

if (regA==regB)

flgZ=1;

else

flgZ=0;

endif

else

if (codec13p)

if (regA==coded)

flgZ=1;

else

flgZ=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.0:7==0)

flgZ=1;

else

flgZ=0;

endif

else

flgZ=flgZ;

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ 加算と減算の入力 }

{ ------------------------------------------------------------------ }

calca.0:7=regA;

switch(codec)

case 16: calcb.0:7=regB;

case 17: calcb.0:7=coded;

case 18: calcb.0:7=regB;

case 19: calcb.0:7=coded;

endswitch

{ ------------------------------------------------------------------ }

{ 加算と減算 }

{ ------------------------------------------------------------------ }

if (codec16p|codec17p) calcy=calca+calcb; endif

if (codec18p|codec19p) calcy=calca-calcb; endif

{ ------------------------------------------------------------------ }

{ 命令デコード }

{ ------------------------------------------------------------------ }

switch(codec)

case 1: codec1p=1; { LD (X),A }

case 2: codec2p=1; { LD A,(X) }

case 3: codec3p=1; { LD A,n }

case 4: codec4p=1; { LD X,n }

case 5: codec5p=1; { CMP A,(X) }

case 6: codec6p=1; { JPC n }

case 7: codec7p=1; { JPNC n }

case 8: codec8p=1; { JPZ n }

case 9: codec9p=1; { JPNZ n }

case 10: codec10p=1; { JP n }

case 11: codec11p=1; { LD B,A }

case 12: codec12p=1; { CMP A,B }

case 13: codec13p=1; { CMP A,n }

case 14: codec14p=1; { INC A }

case 15: codec15p=1; { INC X }

case 16: codec16p=1; { ADD A,B }

case 17: codec17p=1; { ADD A,n }

case 18: codec18p=1; { SUB A,B }

case 19: codec19p=1; { SUB A,n }

case 20: codec20p=1; { LD A,B }

case 21: codec21p=1; { LD X,A }

case 22: codec22p=1; { LD A,X }

case 23: codec23p=1; { LD (X),n }

case 24: codec24p=1; { DEC A }

case 25: codec25p=1; { DEC X }

case 26: codec26p=1; { LD (X),B }

case 27: codec27p=1; { LD B,(X) }

case 28: codec28p=1; { LD X,(X) }

case 29: codec29p=1; { LD A,PORT }

case 30: codec30p=1; { LD PORT,A }

endswitch

ende

{ ================================================================== }

{ 機能実行譜 }

{ ================================================================== }

entity sim

{ ------------------------------------------------------------------ }

{ 実効譜端子 }

{ ------------------------------------------------------------------ }

output reset;

output portin[8];

output data[8];

output address[4];

output cs;

output re;

output we;

output portout[8];

output writedata[8];

{ ------------------------------------------------------------------ }

{ 検査端子 }

{ ------------------------------------------------------------------ }

output TB0P[8];

output TB1P[8];

output TB2P[8];

output TB3P[8];

output TB4P[8];

output TB5P[8];

output TB6P[8];

output TB7P[8];

output TB8P[8];

output TB9P[8];

output TB10P[8];

output TB11P[8];

input simres;

{ ------------------------------------------------------------------ }

{ 内部信号 }

{ ------------------------------------------------------------------ }

bitr tc[12];

bitr memory0d[8];

bitr memory1d[8];

bitr memory2d[8];

bitr memory3d[8];

bitr memory4d[8];

bitr memory5d[8];

bitr memory6d[8];

bitr memory7d[8];

bitr memory8d[8];

bitr memory9d[8];

bitr memory10d[8];

bitr memory11d[8];

bitn node_reset;

bitn node_cs;

bitn node_re;

bitn node_we;

bitn node_address[4];

bitn node_writedata[8];

{ ------------------------------------------------------------------ }

{ 検査端子代入 }

{ ------------------------------------------------------------------ }

TB0P=memory0d;

TB1P=memory1d;

TB2P=memory2d;

TB3P=memory3d;

TB4P=memory4d;

TB5P=memory5d;

TB6P=memory6d;

TB7P=memory7d;

TB8P=memory8d;

TB9P=memory9d;

TB10P=memory10d;

TB11P=memory11d;

{ ------------------------------------------------------------------ }

{ 出力代入 }

{ ------------------------------------------------------------------ }

reset=node_reset;

cs=node_cs;

re=node_re;

we=node_we;

address=node_address;

writedata=node_writedata;

{ ------------------------------------------------------------------ }

{ 実効譜引用 }

{ ------------------------------------------------------------------ }

part main(node_reset,portin,data,node_address,node_cs,node_re,node_we,portout,node_writedata)

{ ------------------------------------------------------------------ }

{ 検査譜 }

{ ------------------------------------------------------------------ }

simres=0;

if (!simres) tc=tc+1; endif

if (tc<5) node_reset=1; endif

if (tc>35) portin=1; endif

{ ------------------------------------------------------------------ }

{ メモリ 0 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory0d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==0)

memory0d=node_writedata;

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 1 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory1d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==1)

memory1d=node_writedata;

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 2 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory2d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==2)

memory2d=node_writedata;

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 3 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory3d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==3)

memory3d=node_writedata;

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 4 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory4d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==4)

memory4d=node_writedata;

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 5 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory5d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==5)

memory5d=node_writedata;

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 6 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory6d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==6)

memory6d=node_writedata;

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 7 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory7d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==7)

memory7d=node_writedata;

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 8 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory8d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==8)

memory8d=node_writedata;

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 9 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory9d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==9)

memory9d=node_writedata;

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 10 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory10d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==10)

memory10d=node_writedata;

else

memory10d=memory10d;

endif

else

memory10d=memory10d;

endif

else

memory10d=memory10d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 11 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory11d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==11)

memory11d=node_writedata;

else

memory11d=memory11d;

endif

else

memory11d=memory11d;

endif

else

memory11d=memory11d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ出力 }

{ ------------------------------------------------------------------ }

if (!node_cs&!node_re)

switch(node_address)

case 0: data=memory0d;

case 1: data=memory1d;

case 2: data=memory2d;

case 3: data=memory3d;

case 4: data=memory4d;

case 5: data=memory5d;

case 6: data=memory6d;

case 7: data=memory7d;

case 8: data=memory8d;

case 9: data=memory9d;

case 10: data=memory10d;

case 11: data=memory11d;

endswitch

endif

ende

endlogic

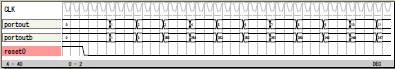

その2

並び替え用に作った8ビットプロセッサはプログラム内蔵型で

した。汎用的に使うためにプログラムを外置きにしてみました

。小規模の用途に限定しても汎用プロセッサに比べると命令の

種類が足りません例えば論理演算やシフト、サブルーチンコー

ルなどもありません。しかしプログラムの決まっている専用プ

ロセッサに一般的な命令を全部そろえる必要はありませんでし

た。プログラムの作成時に必要に応じて足していっても構わな

い訳です。今回のプロセッサはプログラム内蔵型でXilinxのXC95216

に入りましたプログラム外置き型でXC95288に入りました。プ

ログラム内蔵型の場合はプログラムで使っていないプロセッサ

の構造が最適化されるのでプログラム外置きのプロセッサより

は小さくできます。プログラムをメモリ方式以外の論理的な方

法で実装することでプロセッサの構造をプログラムと一体に最

適化できるので色々の場面で使用できると思います。なにより

短時間にプロセッサを作ることができるので専用プロセッサを

色々作ってみたいと思います。

file: sample28

論理譜

logicname yahoo39

{ ================================================================== }

{ 実効譜 }

{ ================================================================== }

entity main

{ ------------------------------------------------------------------ }

{ 入力端子 }

{ ------------------------------------------------------------------ }

input reset;

input portin[8];

input codedata[16];

{ ------------------------------------------------------------------ }

{ 双方向端子 }

{ ------------------------------------------------------------------ }

inout data[8];

{ ------------------------------------------------------------------ }

{ 出力端子 }

{ ------------------------------------------------------------------ }

output address[4];

output cs;

output re;

output we;

output portout[8];

output writedata[8];

output codeaddress[8];

{ ------------------------------------------------------------------ }

{ 内部信号 }

{ ------------------------------------------------------------------ }

bitn datain[8];

bitn dataout[8];

bitn datacnt;

bitr codepoint[8];

bitn codec[8];

bitn coded[8];

bitr regA[8];

bitr regB[8];

bitr regX[8];

bitr flgC;

bitr flgZ;

bitr regport[8];

bitn codec1p;

bitn codec2p;

bitn codec3p;

bitn codec4p;

bitn codec5p;

bitn codec6p;

bitn codec7p;

bitn codec8p;

bitn codec9p;

bitn codec10p;

bitn codec11p;

bitn codec12p;

bitn codec13p;

bitn codec14p;

bitn codec15p;

bitn codec16p;

bitn codec17p;

bitn codec18p;

bitn codec19p;

bitn codec20p;

bitn codec21p;

bitn codec22p;

bitn codec23p;

bitn codec24p;

bitn codec25p;

bitn codec26p;

bitn codec27p;

bitn codec28p;

bitn codec29p;

bitn codec30p;

bitn calcy[9];

bitn calca[9];

bitn calcb[9];

bitr wseq[2];

{ ------------------------------------------------------------------ }

{ 検査端子 }

{ ------------------------------------------------------------------ }

{}

output T0P[8]; T0P=codepoint;

output T1P[8]; T1P=regB;

output T2P[8]; T2P=regA;

output T3P[8]; T3P=regX;

output T4P; T4P=flgZ;

output T5P[8]; T5P=codec;

output T6P[8]; T6P=coded;

{}

{ ------------------------------------------------------------------ }

{ 出力代入 }

{ ------------------------------------------------------------------ }

address=regX.0:3;

writedata=dataout;

we=!(datacnt&(wseq==1));

re=!(codec2p|codec5p|codec27p|codec28p);

cs=!(codec1p|codec2p|codec5p|codec23p|codec26p|codec27p|codec28p);

portout=regport;

codeaddress=codepoint;

{ ------------------------------------------------------------------ }

{ データバス設定 }

{ ------------------------------------------------------------------ }

enable(data,datain,dataout,datacnt)

datain.8=1;

{ ------------------------------------------------------------------ }

{ メモリデータ出力 }

{ ------------------------------------------------------------------ }

switch(codec)

case 1: dataout=regA;

case 23: dataout=coded;

case 26: dataout=regB;

endswitch

{ ------------------------------------------------------------------ }

{ メモリデータバス制御 }

{ ------------------------------------------------------------------ }

if (codec1p|codec23p|codec26p) datacnt=1; endif

{ ------------------------------------------------------------------ }

{ 書き込み進行計数 }

{ ------------------------------------------------------------------ }

if (reset)

wseq=0;

else

if (datacnt)

wseq=wseq+1;

else

wseq=0;

endif

endif

{ ------------------------------------------------------------------ }

{ 命令ポインタ }

{ ------------------------------------------------------------------ }

if (reset)

codepoint=0;

else

if (codec6p&flgC)

codepoint=coded;

else

if (codec7p&!flgC)

codepoint=coded;

else

if (codec8p&flgZ)

codepoint=coded;

else

if (codec9p&!flgZ)

codepoint=coded;

else

if (codec10p)

codepoint=coded;

else

if (datacnt)

if (wseq==2)

codepoint=codepoint+1;

else

codepoint=codepoint;

endif

else

codepoint=codepoint+1;

endif

endif

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ プログラム }

{ ------------------------------------------------------------------ }

codec=codedata.0:7;

coded=codedata.8:15;

{ ------------------------------------------------------------------ }

{ 出力ポート }

{ ------------------------------------------------------------------ }

if (reset)

regport=0;

else

if (codec30p)

regport=regA;

else

regport=regport;

endif

endif

{ ------------------------------------------------------------------ }

{ 主レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regA=0;

else

switch(codec)

case 2: regA=datain;

case 3: regA=coded;

case 14: regA=regA+1;

case 20: regA=regB;

case 22: regA=regX;

case 24: regA=regA-1;

case 29: regA=portin;

default: regA=regA;

endswitch

endif

{ ------------------------------------------------------------------ }

{ 補助レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regB=0;

else

switch(codec)

case 11: regB=regA;

case 27: regB=datain;

default: regB=regB;

endswitch

endif

{ ------------------------------------------------------------------ }

{ 番地レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regX=0;

else

switch(codec)

case 4: regX=coded;

case 15: regX=regX+1;

case 21: regX=regA;

case 25: regX=regX-1;

case 28: regX=datain;

default: regX=regX;

endswitch

endif

{ ------------------------------------------------------------------ }

{ キャリーフラグ }

{ ------------------------------------------------------------------ }

if (reset)

flgC=0;

else

if (codec5p)

if (regA<datain)

flgC=1;

else

flgC=0;

endif

else

if (codec12p)

if (regA<regB)

flgC=1;

else

flgC=0;

endif

else

if (codec13p)

if (regA<coded)

flgC=1;

else

flgC=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.8)

flgC=1;

else

flgC=0;

endif

else

flgC=flgC;

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ ゼロフラグ }

{ ------------------------------------------------------------------ }

if (reset)

flgZ=0;

else

if (codec5p)

if (regA==datain)

flgZ=1;

else

flgZ=0;

endif

else

if (codec12p)

if (regA==regB)

flgZ=1;

else

flgZ=0;

endif

else

if (codec13p)

if (regA==coded)

flgZ=1;

else

flgZ=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.0:7==0)

flgZ=1;

else

flgZ=0;

endif

else

flgZ=flgZ;

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ 加算と減算の入力 }

{ ------------------------------------------------------------------ }

calca.0:7=regA;

switch(codec)

case 16: calcb.0:7=regB;

case 17: calcb.0:7=coded;

case 18: calcb.0:7=regB;

case 19: calcb.0:7=coded;

endswitch

{ ------------------------------------------------------------------ }

{ 加算と減算 }

{ ------------------------------------------------------------------ }

if (codec16p|codec17p) calcy=calca+calcb; endif

if (codec18p|codec19p) calcy=calca-calcb; endif

{ ------------------------------------------------------------------ }

{ 命令デコード }

{ ------------------------------------------------------------------ }

switch(codec)

case 1: codec1p=1; { LD (X),A }

case 2: codec2p=1; { LD A,(X) }

case 3: codec3p=1; { LD A,n }

case 4: codec4p=1; { LD X,n }

case 5: codec5p=1; { CMP A,(X) }

case 6: codec6p=1; { JPC n }

case 7: codec7p=1; { JPNC n }

case 8: codec8p=1; { JPZ n }

case 9: codec9p=1; { JPNZ n }

case 10: codec10p=1; { JP n }

case 11: codec11p=1; { LD B,A }

case 12: codec12p=1; { CMP A,B }

case 13: codec13p=1; { CMP A,n }

case 14: codec14p=1; { INC A }

case 15: codec15p=1; { INC X }

case 16: codec16p=1; { ADD A,B }

case 17: codec17p=1; { ADD A,n }

case 18: codec18p=1; { SUB A,B }

case 19: codec19p=1; { SUB A,n }

case 20: codec20p=1; { LD A,B }

case 21: codec21p=1; { LD X,A }

case 22: codec22p=1; { LD A,X }

case 23: codec23p=1; { LD (X),n }

case 24: codec24p=1; { DEC A }

case 25: codec25p=1; { DEC X }

case 26: codec26p=1; { LD (X),B }

case 27: codec27p=1; { LD B,(X) }

case 28: codec28p=1; { LD X,(X) }

case 29: codec29p=1; { LD A,PORT }

case 30: codec30p=1; { LD PORT,A }

endswitch

ende

{ ================================================================== }

{ 機能実行譜 }

{ ================================================================== }

entity sim

{ ------------------------------------------------------------------ }

{ 実効譜端子 }

{ ------------------------------------------------------------------ }

output reset;

output portin[8];

output codedata[16];

output data[8];

output address[4];

output cs;

output re;

output we;

output portout[8];

output writedata[8];

output codeaddress[8];

input simres;

{ ------------------------------------------------------------------ }

{ 検査端子 }

{ ------------------------------------------------------------------ }

output TB0P[8];

output TB1P[8];

output TB2P[8];

output TB3P[8];

output TB4P[8];

output TB5P[8];

output TB6P[8];

output TB7P[8];

output TB8P[8];

output TB9P[8];

output TB10P[8];

output TB11P[8];

{ ------------------------------------------------------------------ }

{ 内部信号 }

{ ------------------------------------------------------------------ }

bitr tc[12];

bitr memory0d[8];

bitr memory1d[8];

bitr memory2d[8];

bitr memory3d[8];

bitr memory4d[8];

bitr memory5d[8];

bitr memory6d[8];

bitr memory7d[8];

bitr memory8d[8];

bitr memory9d[8];

bitr memory10d[8];

bitr memory11d[8];

bitn node_reset;

bitn node_cs;

bitn node_re;

bitn node_we;

bitn node_address[4];

bitn node_writedata[8];

bitn node_codeaddress[8];

{ ------------------------------------------------------------------ }

{ 検査端子代入 }

{ ------------------------------------------------------------------ }

TB0P=memory0d;

TB1P=memory1d;

TB2P=memory2d;

TB3P=memory3d;

TB4P=memory4d;

TB5P=memory5d;

TB6P=memory6d;

TB7P=memory7d;

TB8P=memory8d;

TB9P=memory9d;

TB10P=memory10d;

TB11P=memory11d;

{ ------------------------------------------------------------------ }

{ 出力代入 }

{ ------------------------------------------------------------------ }

reset=node_reset;

cs=node_cs;

re=node_re;

we=node_we;

address=node_address;

writedata=node_writedata;

codeaddress=node_codeaddress;

{ ------------------------------------------------------------------ }

{ 実効譜引用 }

{ ------------------------------------------------------------------ }

part main(node_reset,portin,codedata,data,node_address,node_cs

,node_re,node_we,portout,node_writedata,node_codeaddress)

{ ------------------------------------------------------------------ }

{ 検査譜 }

{ ------------------------------------------------------------------ }

simres=0;

if (!simres) tc=tc+1; endif

if (tc<5) node_reset=1; endif

if (tc>35) portin=1; endif

{ ------------------------------------------------------------------ }

{ メモリ 0 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory0d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==0)

memory0d=node_writedata;

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

else

memory0d=memory0d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 1 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory1d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==1)

memory1d=node_writedata;

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

else

memory1d=memory1d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 2 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory2d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==2)

memory2d=node_writedata;

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

else

memory2d=memory2d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 3 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory3d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==3)

memory3d=node_writedata;

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

else

memory3d=memory3d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 4 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory4d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==4)

memory4d=node_writedata;

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

else

memory4d=memory4d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 5 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory5d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==5)

memory5d=node_writedata;

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

else

memory5d=memory5d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 6 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory6d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==6)

memory6d=node_writedata;

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

else

memory6d=memory6d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 7 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory7d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==7)

memory7d=node_writedata;

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

else

memory7d=memory7d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 8 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory8d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==8)

memory8d=node_writedata;

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

else

memory8d=memory8d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 9 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory9d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==9)

memory9d=node_writedata;

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

else

memory9d=memory9d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 10 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory10d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==10)

memory10d=node_writedata;

else

memory10d=memory10d;

endif

else

memory10d=memory10d;

endif

else

memory10d=memory10d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ 11 }

{ ------------------------------------------------------------------ }

if (node_reset)

memory11d=0;

else

if (!node_cs)

if (!node_we)

if (node_address==11)

memory11d=node_writedata;

else

memory11d=memory11d;

endif

else

memory11d=memory11d;

endif

else

memory11d=memory11d;

endif

endif

{ ------------------------------------------------------------------ }

{ メモリ出力 }

{ ------------------------------------------------------------------ }

if (!node_cs&!node_re)

switch(node_address)

case 0: data=memory0d;

case 1: data=memory1d;

case 2: data=memory2d;

case 3: data=memory3d;

case 4: data=memory4d;

case 5: data=memory5d;

case 6: data=memory6d;

case 7: data=memory7d;

case 8: data=memory8d;

case 9: data=memory9d;

case 10: data=memory10d;

case 11: data=memory11d;

endswitch

endif

{ ------------------------------------------------------------------ }

{ プログラム }

{ ------------------------------------------------------------------ }

switch(node_codeaddress)

case 0: codedata.0:7=0; codedata.8:15=0;

case 1: codedata.0:7=23; codedata.8:15=17; { LD (X),17 }

case 2: codedata.0:7=4; codedata.8:15=1; { LD X,1 }

case 3: codedata.0:7=23; codedata.8:15=16; { LD (X),16 }

case 4: codedata.0:7=4; codedata.8:15=2; { LD X,2 }

case 5: codedata.0:7=23; codedata.8:15=15; { LD (X),15 }

case 6: codedata.0:7=4; codedata.8:15=3; { LD X,3 }

case 7: codedata.0:7=23; codedata.8:15=14; { LD (X),14 }

case 8: codedata.0:7=4; codedata.8:15=4; { LD X,4 }

case 9: codedata.0:7=23; codedata.8:15=13; { LD (X),13 }

case 10: codedata.0:7=4; codedata.8:15=5; { LD X,5 }

case 11: codedata.0:7=23; codedata.8:15=12; { LD (X),12 }

case 12: codedata.0:7=4; codedata.8:15=6; { LD X,6 }

case 13: codedata.0:7=23; codedata.8:15=11; { LD (X),11 }

case 14: codedata.0:7=4; codedata.8:15=7; { LD X,7 }

case 15: codedata.0:7=23; codedata.8:15=10; { LD (X),10 }

case 16: codedata.0:7=4; codedata.8:15=8; { LD X,8 }

case 17: codedata.0:7=23; codedata.8:15=9; { LD (X),9 }

case 18: codedata.0:7=4; codedata.8:15=9; { LD X,9 }

case 19: codedata.0:7=23; codedata.8:15=8; { LD (X),8 }

case 20: codedata.0:7=29; { LD A,PORT }

case 21: codedata.0:7=13; codedata.8:15=0; { CMP A,0 }

case 22: codedata.0:7=8; codedata.8:15=20; { JPZ 20 }

case 23: codedata.0:7=4; codedata.8:15=10; { LD X,10 }

case 24: codedata.0:7=28; { LD X,(X) }

case 25: codedata.0:7=2; { LD A,(X) }

case 26: codedata.0:7=15; { INC X }

case 27: codedata.0:7=5; { CMP A,(X) }

case 28: codedata.0:7=6; codedata.8:15=49; { JPC 49 }

case 29: codedata.0:7=27; { LD B,(X) }

case 30: codedata.0:7=1; { LD (X),A }

case 31: codedata.0:7=25; { DEC X }

case 32: codedata.0:7=26; { LD (X),B }

case 33: codedata.0:7=22; { LD A,X }

case 34: codedata.0:7=4; codedata.8:15=11; { LD X,11 }

case 35: codedata.0:7=23; codedata.8:15=255; { LD (X),0FFh }

case 36: codedata.0:7=21; { LD X,A }

case 37: codedata.0:7=10; codedata.8:15=49; { JP 49 }

case 49: codedata.0:7=15; { INC X }

case 50: codedata.0:7=22; { LD A,X }

case 51: codedata.0:7=13; codedata.8:15=9; { CMP A,9 }

case 52: codedata.0:7=6; codedata.8:15=60; { JPC 60 }

case 53: codedata.0:7=4; codedata.8:15=11; { LD X,11 }

case 54: codedata.0:7=3; codedata.8:15=0; { LD A,0 }

case 55: codedata.0:7=5; { CMP A,(X) }

case 56: codedata.0:7=8; codedata.8:15=70; { JPZ 70 }

case 57: codedata.0:7=23; codedata.8:15=0; { LD (X),0 }

case 58: codedata.0:7=3; codedata.8:15=0; { LD A,0 }

case 60: codedata.0:7=4; codedata.8:15=10; { LD X,10 }

case 61: codedata.0:7=1; { LD (X),A }

case 62: codedata.0:7=10; codedata.8:15=23; { JP 23 }

case 70: codedata.0:7=3; codedata.8:15=1; { LD A,1 }

case 71: codedata.0:7=30; { LD PORT,A }

case 72: codedata.0:7=10; codedata.8:15=72; { JP 72 }

endswitch

ende

endlogic

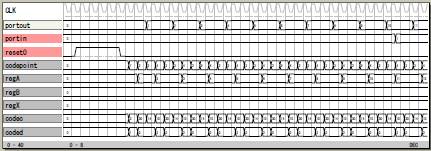

その3

チップCLKを計数して8ビットのポートに出力するだけの数行の

プログラムを作ってみました。レジスタのみを使いメモリは使

っていませんがXilinxのXC9536にフィッティングできました。

file: sample29

論理譜

logicname yahoo40

{ ================================================================== }

{ 実効譜 }

{ ================================================================== }

entity main

{ ------------------------------------------------------------------ }

{ 入力端子 }

{ ------------------------------------------------------------------ }

input reset;

input portin[8];

{ ------------------------------------------------------------------ }

{ 出力端子 }

{ ------------------------------------------------------------------ }

output portout[8];

{ ------------------------------------------------------------------ }

{ 内部信号 }

{ ------------------------------------------------------------------ }

bitn datain[8];

bitn dataout[8];

bitn datacnt;

bitr codepoint[8];

bitn codec[8];

bitn coded[8];

bitr regA[8];

bitr regB[8];

bitr regX[8];

bitr flgC;

bitr flgZ;

bitr regport[8];

bitn codec1p;

bitn codec2p;

bitn codec3p;

bitn codec4p;

bitn codec5p;

bitn codec6p;

bitn codec7p;

bitn codec8p;

bitn codec9p;

bitn codec10p;

bitn codec11p;

bitn codec12p;

bitn codec13p;

bitn codec14p;

bitn codec15p;

bitn codec16p;

bitn codec17p;

bitn codec18p;

bitn codec19p;

bitn codec20p;

bitn codec21p;

bitn codec22p;

bitn codec23p;

bitn codec24p;

bitn codec25p;

bitn codec26p;

bitn codec27p;

bitn codec28p;

bitn codec29p;

bitn codec30p;

bitn calcy[9];

bitn calca[9];

bitn calcb[9];

bitr wseq[2];

{ ------------------------------------------------------------------ }

{ 検査端子 }

{ ------------------------------------------------------------------ }

{}

output T0P[8]; T0P=codepoint;

output T1P[8]; T1P=regB;

output T2P[8]; T2P=regA;

output T3P[8]; T3P=regX;

output T4P; T4P=flgZ;

output T5P[8]; T5P=codec;

output T6P[8]; T6P=coded;

{}

{ ------------------------------------------------------------------ }

{ 出力代入 }

{ ------------------------------------------------------------------ }

portout=regport;

{ ------------------------------------------------------------------ }

{ メモリデータ出力 }

{ ------------------------------------------------------------------ }

switch(codec)

case 1: dataout=regA;

case 23: dataout=coded;

case 26: dataout=regB;

endswitch

{ ------------------------------------------------------------------ }

{ メモリデータ書き込み }

{ ------------------------------------------------------------------ }

if (codec1p|codec23p|codec26p) datacnt=1; endif

{ ------------------------------------------------------------------ }

{ 書き込み進行計数 }

{ ------------------------------------------------------------------ }

if (reset)

wseq=0;

else

if (datacnt)

wseq=wseq+1;

else

wseq=0;

endif

endif

{ ------------------------------------------------------------------ }

{ 命令ポインタ }

{ ------------------------------------------------------------------ }

if (reset)

codepoint=0;

else

if (codec6p&flgC)

codepoint=coded;

else

if (codec7p&!flgC)

codepoint=coded;

else

if (codec8p&flgZ)

codepoint=coded;

else

if (codec9p&!flgZ)

codepoint=coded;

else

if (codec10p)

codepoint=coded;

else

if (datacnt)

if (wseq==2)

codepoint=codepoint+1;

else

codepoint=codepoint;

endif

else

codepoint=codepoint+1;

endif

endif

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ プログラム }

{ ------------------------------------------------------------------ }

switch(codepoint)

case 1: codec=3; coded=1; { LD A,1 }

case 2: codec=30; { LD PORT,A }

case 3: codec=14; { INC A }

case 4: codec=10; coded=2; { JP 2 }

endswitch

{ ------------------------------------------------------------------ }

{ 出力ポート }

{ ------------------------------------------------------------------ }

if (reset)

regport=0;

else

if (codec30p)

regport=regA;

else

regport=regport;

endif

endif

{ ------------------------------------------------------------------ }

{ 主レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regA=0;

else

switch(codec)

case 2: regA=datain;

case 3: regA=coded;

case 14: regA=regA+1;

case 20: regA=regB;

case 22: regA=regX;

case 24: regA=regA-1;

case 29: regA=portin;

default: regA=regA;

endswitch

endif

{ ------------------------------------------------------------------ }

{ 補助レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regB=0;

else

switch(codec)

case 11: regB=regA;

case 27: regB=datain;

default: regB=regB;

endswitch

endif

{ ------------------------------------------------------------------ }

{ 番地レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regX=0;

else

switch(codec)

case 4: regX=coded;

case 15: regX=regX+1;

case 21: regX=regA;

case 25: regX=regX-1;

case 28: regX=datain;

default: regX=regX;

endswitch

endif

{ ------------------------------------------------------------------ }

{ キャリーフラグ }

{ ------------------------------------------------------------------ }

if (reset)

flgC=0;

else

if (codec5p)

if (regA<datain)

flgC=1;

else

flgC=0;

endif

else

if (codec12p)

if (regA<regB)

flgC=1;

else

flgC=0;

endif

else

if (codec13p)

if (regA<coded)

flgC=1;

else

flgC=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.8)

flgC=1;

else

flgC=0;

endif

else

flgC=flgC;

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ ゼロフラグ }

{ ------------------------------------------------------------------ }

if (reset)

flgZ=0;

else

if (codec5p)

if (regA==datain)

flgZ=1;

else

flgZ=0;

endif

else

if (codec12p)

if (regA==regB)

flgZ=1;

else

flgZ=0;

endif

else

if (codec13p)

if (regA==coded)

flgZ=1;

else

flgZ=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.0:7==0)

flgZ=1;

else

flgZ=0;

endif

else

flgZ=flgZ;

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ 加算と減算の入力 }

{ ------------------------------------------------------------------ }

calca.0:7=regA;

switch(codec)

case 16: calcb.0:7=regB;

case 17: calcb.0:7=coded;

case 18: calcb.0:7=regB;

case 19: calcb.0:7=coded;

endswitch

{ ------------------------------------------------------------------ }

{ 加算と減算 }

{ ------------------------------------------------------------------ }

if (codec16p|codec17p) calcy=calca+calcb; endif

if (codec18p|codec19p) calcy=calca-calcb; endif

{ ------------------------------------------------------------------ }

{ 命令デコード }

{ ------------------------------------------------------------------ }

switch(codec)

case 1: codec1p=1; { LD (X),A }

case 2: codec2p=1; { LD A,(X) }

case 3: codec3p=1; { LD A,n }

case 4: codec4p=1; { LD X,n }

case 5: codec5p=1; { CMP A,(X) }

case 6: codec6p=1; { JPC n }

case 7: codec7p=1; { JPNC n }

case 8: codec8p=1; { JPZ n }

case 9: codec9p=1; { JPNZ n }

case 10: codec10p=1; { JP n }

case 11: codec11p=1; { LD B,A }

case 12: codec12p=1; { CMP A,B }

case 13: codec13p=1; { CMP A,n }

case 14: codec14p=1; { INC A }

case 15: codec15p=1; { INC X }

case 16: codec16p=1; { ADD A,B }

case 17: codec17p=1; { ADD A,n }

case 18: codec18p=1; { SUB A,B }

case 19: codec19p=1; { SUB A,n }

case 20: codec20p=1; { LD A,B }

case 21: codec21p=1; { LD X,A }

case 22: codec22p=1; { LD A,X }

case 23: codec23p=1; { LD (X),n }

case 24: codec24p=1; { DEC A }

case 25: codec25p=1; { DEC X }

case 26: codec26p=1; { LD (X),B }

case 27: codec27p=1; { LD B,(X) }

case 28: codec28p=1; { LD X,(X) }

case 29: codec29p=1; { LD A,PORT }

case 30: codec30p=1; { LD PORT,A }

endswitch

ende

{ ================================================================== }

{ 機能実行譜 }

{ ================================================================== }

entity sim

{ ------------------------------------------------------------------ }

{ 実効譜端子 }

{ ------------------------------------------------------------------ }

output reset;

output portin[8];

output portout[8];

input simres;

{ ------------------------------------------------------------------ }

{ 内部信号 }

{ ------------------------------------------------------------------ }

bitr tc[12];

{ ------------------------------------------------------------------ }

{ 実効譜引用 }

{ ------------------------------------------------------------------ }

part main(reset,portin,portout)

{ ------------------------------------------------------------------ }

{ 検査譜 }

{ ------------------------------------------------------------------ }

simres=0;

if (!simres) tc=tc+1; endif

if (tc<5) reset=1; endif

if (tc>35) portin=1; endif

ende

endlogic

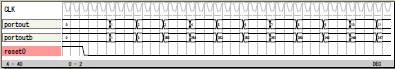

その4

プロセッサを手続きにしました。手続きを2箇所で引用してプ

ロセッサAとプロセッサBで違うプログラムを実装することがで

きます。同一の論理譜内なので共有の信号を持たせることも簡

単です。本例では同一仕様のマルチプロセッサですが違う仕様

のマルチプロセッサにすることもできます。

本例のプロセッサのプログラムは簡単なものですがXilinxのXC9572

に入りました。

file: sample30

論理譜

logicname yahoo41

{ ================================================================== }

{ 手続き譜 }

{ ================================================================== }

{ ================================================================== }

{ プロセッサ }

{ ================================================================== }

procedure pross

{ ------------------------------------------------------------------ }

{ 入力端子 }

{ ------------------------------------------------------------------ }

input reset;

input data[16];

input portin[8];

{ ------------------------------------------------------------------ }

{ 出力端子 }

{ ------------------------------------------------------------------ }

output q[16];

{ ------------------------------------------------------------------ }

{ 内部信号 }

{ ------------------------------------------------------------------ }

bitn datain[8];

bitn dataout[8];

bitn datacnt;

bitr codepoint[8];

bitn codec[8];

bitn coded[8];

bitr regA[8];

bitr regB[8];

bitr regX[8];

bitr flgC;

bitr flgZ;

bitr regport[8];

bitn codec1p;

bitn codec2p;

bitn codec3p;

bitn codec4p;

bitn codec5p;

bitn codec6p;

bitn codec7p;

bitn codec8p;

bitn codec9p;

bitn codec10p;

bitn codec11p;

bitn codec12p;

bitn codec13p;

bitn codec14p;

bitn codec15p;

bitn codec16p;

bitn codec17p;

bitn codec18p;

bitn codec19p;

bitn codec20p;

bitn codec21p;

bitn codec22p;

bitn codec23p;

bitn codec24p;

bitn codec25p;

bitn codec26p;

bitn codec27p;

bitn codec28p;

bitn codec29p;

bitn codec30p;

bitn calcy[9];

bitn calca[9];

bitn calcb[9];

bitr wseq[2];

{ ------------------------------------------------------------------ }

{ 出力代入 }

{ ------------------------------------------------------------------ }

q.8:15=regport;

q.0:7=codepoint;

{ ------------------------------------------------------------------ }

{ メモリデータ出力 }

{ ------------------------------------------------------------------ }

switch(codec)

case 1: dataout=regA;

case 23: dataout=coded;

case 26: dataout=regB;

endswitch

{ ------------------------------------------------------------------ }

{ メモリデータ書き込み }

{ ------------------------------------------------------------------ }

if (codec1p|codec23p|codec26p) datacnt=1; endif

{ ------------------------------------------------------------------ }

{ 書き込み進行計数 }

{ ------------------------------------------------------------------ }

if (reset)

wseq=0;

else

if (datacnt)

wseq=wseq+1;

else

wseq=0;

endif

endif

{ ------------------------------------------------------------------ }

{ 命令ポインタ }

{ ------------------------------------------------------------------ }

if (reset)

codepoint=0;

else

if (codec6p&flgC)

codepoint=coded;

else

if (codec7p&!flgC)

codepoint=coded;

else

if (codec8p&flgZ)

codepoint=coded;

else

if (codec9p&!flgZ)

codepoint=coded;

else

if (codec10p)

codepoint=coded;

else

if (datacnt)

if (wseq==2)

codepoint=codepoint+1;

else

codepoint=codepoint;

endif

else

codepoint=codepoint+1;

endif

endif

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ プログラム }

{ ------------------------------------------------------------------ }

codec=data.0:7;

coded=data.8:15;

{ ------------------------------------------------------------------ }

{ 出力ポート }

{ ------------------------------------------------------------------ }

if (reset)

regport=0;

else

if (codec30p)

regport=regA;

else

regport=regport;

endif

endif

{ ------------------------------------------------------------------ }

{ 主レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regA=0;

else

switch(codec)

case 2: regA=datain;

case 3: regA=coded;

case 14: regA=regA+1;

case 20: regA=regB;

case 22: regA=regX;

case 24: regA=regA-1;

case 29: regA=portin;

default: regA=regA;

endswitch

endif

{ ------------------------------------------------------------------ }

{ 補助レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regB=0;

else

switch(codec)

case 11: regB=regA;

case 27: regB=datain;

default: regB=regB;

endswitch

endif

{ ------------------------------------------------------------------ }

{ 番地レジスタ }

{ ------------------------------------------------------------------ }

if (reset)

regX=0;

else

switch(codec)

case 4: regX=coded;

case 15: regX=regX+1;

case 21: regX=regA;

case 25: regX=regX-1;

case 28: regX=datain;

default: regX=regX;

endswitch

endif

{ ------------------------------------------------------------------ }

{ キャリーフラグ }

{ ------------------------------------------------------------------ }

if (reset)

flgC=0;

else

if (codec5p)

if (regA<datain)

flgC=1;

else

flgC=0;

endif

else

if (codec12p)

if (regA<regB)

flgC=1;

else

flgC=0;

endif

else

if (codec13p)

if (regA<coded)

flgC=1;

else

flgC=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.8)

flgC=1;

else

flgC=0;

endif

else

flgC=flgC;

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ ゼロフラグ }

{ ------------------------------------------------------------------ }

if (reset)

flgZ=0;

else

if (codec5p)

if (regA==datain)

flgZ=1;

else

flgZ=0;

endif

else

if (codec12p)

if (regA==regB)

flgZ=1;

else

flgZ=0;

endif

else

if (codec13p)

if (regA==coded)

flgZ=1;

else

flgZ=0;

endif

else

if (codec16p|codec17p|codec18p|codec19p)

if (calcy.0:7==0)

flgZ=1;

else

flgZ=0;

endif

else

flgZ=flgZ;

endif

endif

endif

endif

endif

{ ------------------------------------------------------------------ }

{ 加算と減算の入力 }

{ ------------------------------------------------------------------ }

calca.0:7=regA;

switch(codec)

case 16: calcb.0:7=regB;

case 17: calcb.0:7=coded;

case 18: calcb.0:7=regB;

case 19: calcb.0:7=coded;

endswitch

{ ------------------------------------------------------------------ }

{ 加算と減算 }

{ ------------------------------------------------------------------ }

if (codec16p|codec17p) calcy=calca+calcb; endif

if (codec18p|codec19p) calcy=calca-calcb; endif

{ ------------------------------------------------------------------ }

{ 命令デコード }

{ ------------------------------------------------------------------ }

switch(codec)

case 1: codec1p=1; { LD (X),A }

case 2: codec2p=1; { LD A,(X) }

case 3: codec3p=1; { LD A,n }

case 4: codec4p=1; { LD X,n }

case 5: codec5p=1; { CMP A,(X) }

case 6: codec6p=1; { JPC n }

case 7: codec7p=1; { JPNC n }

case 8: codec8p=1; { JPZ n }

case 9: codec9p=1; { JPNZ n }

case 10: codec10p=1; { JP n }

case 11: codec11p=1; { LD B,A }

case 12: codec12p=1; { CMP A,B }

case 13: codec13p=1; { CMP A,n }

case 14: codec14p=1; { INC A }

case 15: codec15p=1; { INC X }

case 16: codec16p=1; { ADD A,B }

case 17: codec17p=1; { ADD A,n }

case 18: codec18p=1; { SUB A,B }

case 19: codec19p=1; { SUB A,n }

case 20: codec20p=1; { LD A,B }

case 21: codec21p=1; { LD X,A }

case 22: codec22p=1; { LD A,X }

case 23: codec23p=1; { LD (X),n }

case 24: codec24p=1; { DEC A }

case 25: codec25p=1; { DEC X }

case 26: codec26p=1; { LD (X),B }

case 27: codec27p=1; { LD B,(X) }

case 28: codec28p=1; { LD X,(X) }

case 29: codec29p=1; { LD A,PORT }

case 30: codec30p=1; { LD PORT,A }

endswitch

endp

{ ================================================================== }

{ 実効譜 }

{ ================================================================== }

entity main

{ ------------------------------------------------------------------ }

{ 入力端子 }

{ ------------------------------------------------------------------ }

input reset;

{ ------------------------------------------------------------------ }

{ 出力端子 }

{ ------------------------------------------------------------------ }

output port[8];

output portb[8];

{ ------------------------------------------------------------------ }

{ 内部信号 }

{ ------------------------------------------------------------------ }

bitn intpross[16];

bitn codepoint[8];

bitn codec[8];

bitn coded[8];

bitn code[16];

bitn intprossb[16];

bitn codepointb[8];

bitn codebc[8];

bitn codebd[8];

bitn codeb[16];

{ ------------------------------------------------------------------ }

{ プロセッサ A }

{ ------------------------------------------------------------------ }

intpross=pross(reset,code,0);

codepoint=intpross.0:7;

port=intpross.8:15;

code.0:7=codec;

code.8:15=coded;

codepoint=intpross.0:7;

port=intpross.8:15;

switch(codepoint)

case 1: codec=3; coded=1; { LD A,1 }

case 2: codec=30; { LD PORT,A }

case 3: codec=14; { INC A }

case 4: codec=10; coded=2; { JP 2 }

endswitch

{ ------------------------------------------------------------------ }

{ プロセッサ B }

{ ------------------------------------------------------------------ }

intprossb=pross(reset,codeb,0);

codepointb=intprossb.0:7;

portb=intprossb.8:15;

codeb.0:7=codebc;

codeb.8:15=codebd;

switch(codepointb)

case 1: codebc=3; codebd=1; { LD A,1 }

case 2: codebc=30; { LD PORT,A }

case 3: codebc=24; { DEC A }

case 4: codebc=10; codebd=2; { JP 2 }

endswitch

ende

{ ================================================================== }

{ 機能実行譜 }

{ ================================================================== }

entity sim

{ ------------------------------------------------------------------ }

{ 実効譜端子 }

{ ------------------------------------------------------------------ }

output reset;

output portout[8];

output portoutb[8];

input simres;

{ ------------------------------------------------------------------ }

{ 内部信号 }

{ ------------------------------------------------------------------ }

bitr tc[12];

{ ------------------------------------------------------------------ }

{ 実効譜引用 }

{ ------------------------------------------------------------------ }

part main(reset,portout,portoutb)

{ ------------------------------------------------------------------ }

{ 検査譜 }

{ ------------------------------------------------------------------ }

simres=0;

if (!simres) tc=tc+1; endif

if (tc<5) reset=1; endif

ende

endlogic