| 論理設計 | ICチップを作る | No.3 | 論理を作ってみる | DOC08G03A |

|

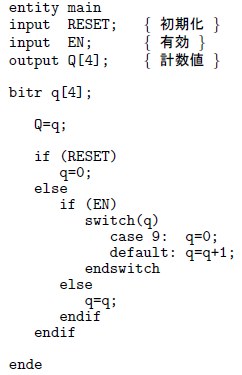

●10進数の計数器

|

左図は前回の実効譜を10進数の計数にしたものです。

q

は4ビットの記憶信号です。

RESET

と

EN

と自分自身の値によって条件付けされています。

条件付けの外側にある信号ほど優先度が高くなりますので

RESET

が1のときは

EN

の値は関係なくなります。

左図の場合は条件信号のすべての値で

q

をどうするかを書いていますがそうでない場合に条件付けにない組み合わせが成立

した場合には

q

は0になります。

EN が0のときの CLK の立ち上がりでは q を計数しません。

EN が1のときの CLK の立ち上がりでは q を計数します。

q が9のときの CLK の立ち上がりでは q は0にされます。 それ以外では前の値に1を加えます。

|

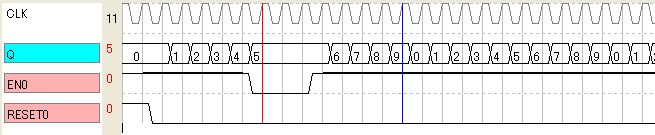

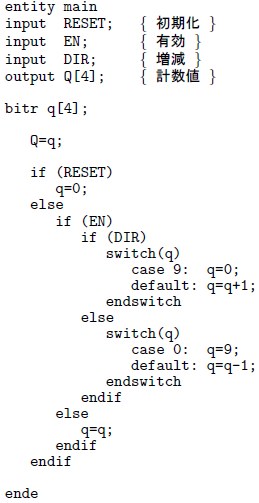

●10進数の増減計数器

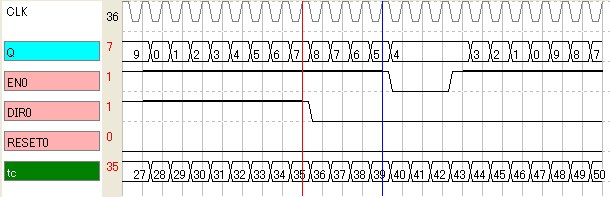

左下の図は上の実効譜を変更して増減計数器にしたものです。 右下の図はその機能実行譜です。

このように簡単な文から始めて必要な機能を追加して複雑な文にしていきます。 この文もブール代数の式や真理値表的な書き方に分解できる訳ですがそれでは論理構造が見えづらくなります 論理設計の論理構造もC言語などの文構造に類似した文で表すことができてブール代数や真理値表と矛盾するところは ありません。

|

|

入力に増減設定の DIR を加えています。 DIR が0のときに減計数で1のときに増計数です。

|

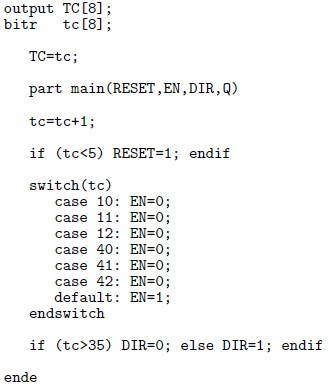

機能実行譜も普通の論理設計です tc は実行位置を示す計数です EN や DIR などの入力値を決定するために使っています。

●機能実行

機能実行で確認することは思ったように動いているかどうかということになります 計数値が10くらいならすべてを確認してもよいのですが16ビットの計数器の計数値 を全部視認することは作業の量からして困難です。 検査の種類は設計者の経験と感で用意するしかなく最終的な結果が思ったとおりな ら途中の行程も思ったとおりに進んでいるはずと思うしかないですが値の確認程度 なら量が多くても変化が一定したものなら機能実行の論理に組み込めます。

絶対に異常な動作をしてはいけない論理の場合には異常な値を記憶した場合の行程 を論理に組み込む訳ですから返って明瞭に機能実行譜を作りやすいと思います。

いずれにしても論理設計の機能実行はすべての信号をCLK単位で追跡できるので大き な論理を設計したときに時間がかかるということはあると思いますが論理的な問題 に限ってはチップに実装してからいつまでたっても動かないということはないと思います。